Spisu treści:

- Krok 1: Budowanie modułu PWM - plik źródłowy

- Krok 2: Budowanie modułu PWM - konfiguracja Vivado

- Krok 3: Budowanie modułu PWM - Utwórz plik projektu

- Krok 4: Budowanie modułu PWM - projekt blokowy i ustawienie pliku z ograniczeniami (I)

- Krok 5: Budowanie modułu PWM - projekt blokowy i ustawienie pliku z ograniczeniami (II)

- Krok 6: Budowanie modułu PWM - projekt blokowy i ustawienie pliku z ograniczeniami (III)

- Krok 7: Budowanie modułu PWM - projekt blokowy i ustawienie pliku z ograniczeniami (IV)

- Krok 8: Budowanie modułu PWM - projekt blokowy i ustawienie pliku z ograniczeniami (V)

- Krok 9: Budowanie modułu PWM - instalacja sprzętu

- Krok 10: Budowanie modułu PWM - wygeneruj strumień bitów i uruchom pakiet SDK

- Krok 11: Budowanie modułu PWM - Utwórz nową aplikację w Xilinx SDK

- Krok 12: Budowanie modułu PWM - przegląd Eksploratora projektów (I)

- Krok 13: Budowanie modułu PWM - przegląd Eksploratora projektów (II)

- Krok 14: Budowanie modułu PWM – przegląd Eksploratora Projektu (III)

- Krok 15: Budowanie modułu PWM - funkcja podsumowania PWM (I)

- Krok 16: Budowanie modułu PWM - funkcja podsumowania PWM (II)

- Krok 17: Budowanie modułu PWM - funkcja podsumowania PWM (III)

- Krok 18: Budowanie modułu PWM - spraw, aby działał

- Krok 19: Strumieniowe przetwarzanie wideo na Digilent ZYBO z OV7670

- Krok 20: Kompletny schemat blokowy

- Krok 21: Podłącz OV7670 do ZYBO

- Krok 22: Utwórz projekt bloku

- Krok 23: Dodaj pliki VHDL do sterowania i przechwytywania kamery OV7670

- Krok 24: Dodaj plik ograniczeń

- Krok 25: Dodaj repozytorium IP dla HLS IP

- Krok 26: Dodaj moduły i adres IP

- Krok 27: Ustawienia konfiguracji IP

- Krok 28: Dodaj i skonfiguruj blokadę IP PS

- Krok 29: Część 1. Budowa modułu PWM dla serwomotorów

- Krok 30: Połączenia po stronie wejścia wideo (podświetlony aklk)

- Krok 31: Połączenia z OV7670

- Krok 32: Połączenia po stronie wyjścia wideo

- Krok 33: Uruchom automatyzację blokowania i połączeń

- Krok 34: Wygeneruj opakowanie HDL

- Krok 35: Wygeneruj strumień bitów, wyeksportuj sprzęt do SDK, uruchom SDK z Vivado

- Krok 36: SDK (bez FreeRTOS)

- Krok 37: Wdrożenie FreeRTOS

- Krok 38: Instrukcja użytkowania

- Krok 39: Odniesienia i linki

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:32.

- Ostatnio zmodyfikowany 2025-06-01 06:10.

Zacznij od kroku pierwszego, aby uzyskać szczegółowe informacje na temat tworzenia 2-osiowego kontrolera serwo PWM.

Zacznij od ogromnego schematu blokowego (krok 19) dla całego projektu.

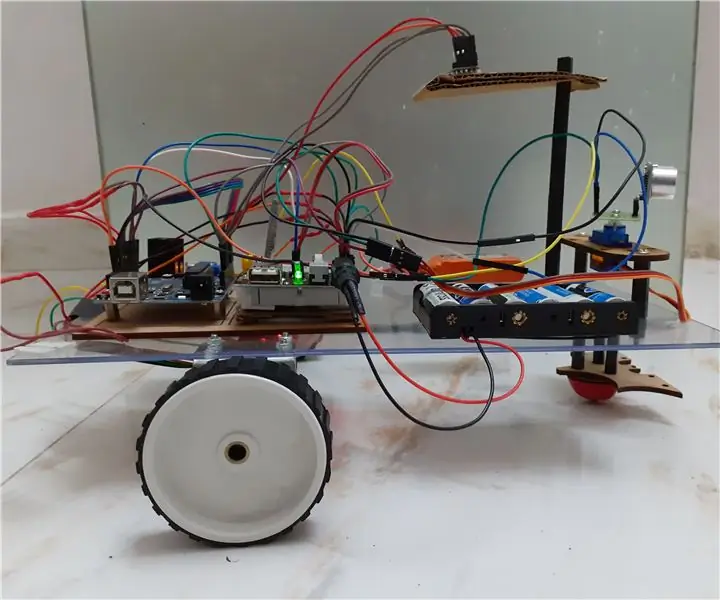

Użyliśmy konfiguracji kamery + Pan/tilt:

Do podłączenia serw wykorzystano PmodCON3 firmy Digilent.

Krok 1: Budowanie modułu PWM - plik źródłowy

Krok 2: Budowanie modułu PWM - konfiguracja Vivado

Najpierw pobierz Vivado Design Suite ze strony Xilinx. Zainstaluj cały pakiet do projektowania, w tym zestaw programistyczny (SDK) firmy Vivado. Ten projekt używa wersji 2017.2.

W międzyczasie Digilent Adept 2 powinien być również zainstalowany jako sterownik płyty Zybo.

Krok 3: Budowanie modułu PWM - Utwórz plik projektu

Przed utworzeniem pliku projektu upewnij się, że plik Zybo został już poprawnie zainstalowany, tak jak w samouczku tutaj:

Instalacja pliku płyty Vivado w wersji 2015.1 i nowszych

Otwórz Vivado 2017.2. W Szybkim starcie kliknij Utwórz projekt -> Dalej -> Nazwa projektu (tu wpisz nazwę swojego projektu) -> Typ projektu. W typie projektu wybierz Projekt RTL i zaznacz „Nie określaj źródeł w tym czasie”. Następnie dla części domyślnej wybierz "Płyty" i "Zybo" jako nazwę wyświetlaną. Następnie kliknij Zakończ, aby rozpocząć projekt.

Krok 4: Budowanie modułu PWM - projekt blokowy i ustawienie pliku z ograniczeniami (I)

W Flow Navigator kliknij „”Utwórz projekt bloku”, a następnie naciśnij OK. kliknij znak „+”, aby dodać niezbędne adresy IP. Dodać:

- Jeden system przetwarzania ZYNQ7 Dwa zegary AXI

- Dwa zegary AXI

Krok 5: Budowanie modułu PWM - projekt blokowy i ustawienie pliku z ograniczeniami (II)

Po dodaniu adresów IP uruchom automatyzację bloków i automatyzację połączeń. Po zakończeniu automatyzacji na bloku „axi_timer_0” kliknij prawym przyciskiem myszy pwm0 -> Make External. Nazwij zewnętrzny pin pwm0 jako pwm_Xaxis. Powtórz również powyższy proces w bloku „axi_timer_1” i nazwij zewnętrzny pin pwm0 jako pwm_Zaxis.

Krok 6: Budowanie modułu PWM - projekt blokowy i ustawienie pliku z ograniczeniami (III)

Zauważ, że za każdym razem, gdy kończymy projektowanie bloków w Vivado, musimy utworzyć opakowanie HDL. Ponieważ będzie to moduł najwyższego poziomu dla każdego projektu.

Krok 7: Budowanie modułu PWM - projekt blokowy i ustawienie pliku z ograniczeniami (IV)

Teraz musimy skonfigurować nasz plik ograniczeń, aby przypisać piny podłączone do naszego schematu blokowego. Zamknij okno Block Design, zakładka On Sources, „Add Sources”->Add or create bounds-> dodaj Zybo-Master.xdc jako nasze pliki z ograniczeniami.

Krok 8: Budowanie modułu PWM - projekt blokowy i ustawienie pliku z ograniczeniami (V)

Otwórz plik ograniczeń Zybo-Master.xdc z folderu Ograniczenia, odkomentuj porty, które chcemy określić jako sygnały wyjściowe i zmień nazwę „ get_ports{XXXX}”, która XXXX oznacza zewnętrzny pin nazwany na schemacie blokowym. Ustawienie pliku wiązania pokazano na rysunku.

Krok 9: Budowanie modułu PWM - instalacja sprzętu

Podłącz serwosilniki do Pmod CON3. TowerPro SG90 to model serwosilnika, którego użyliśmy w tym projekcie. W przypadku przewodów serwomotoru, pomarańczowy przewód reprezentuje sygnał PWM, podłączony do pinu SIG w Pmod CON3. Czerwony przewód Vcc to przewód zasilający podłączony do pinu VS w Pmod CON3. Wreszcie brązowy przewód Gnd jest przewodem uziemiającym podłączonym do pinu GND. Następnie wstaw Pmod CON3 do górnego rzędu portu JD na płycie Zybo.

Krok 10: Budowanie modułu PWM - wygeneruj strumień bitów i uruchom pakiet SDK

1. Na karcie Nawigator projektu uruchom Generuj strumień bitów.

2. Eksportuj sprzęt: Plik > Eksportuj > Eksportuj sprzęt-> zaznacz opcję „włącz strumień bitów”-> OK 3. Uruchom SDK: Plik -> Uruchom SDK.

Krok 11: Budowanie modułu PWM - Utwórz nową aplikację w Xilinx SDK

Stwórz nową aplikację:

Plik > Nowy > Projekt aplikacji -> Wprowadź nazwę swojego projektu -> Zakończ

W Eksploratorze projektów powinny znajdować się trzy foldery.

W tym przypadku „design_1_wrapper_hw_platform_0” to folder wyeksportowany wcześniej przez Vivado. Axis_2_PWM_SDK_bsp to folder pakietu obsługi płyty. A Axis_2_PWM_SDK to nasz główny folder projektu w SDK. Możesz zobaczyć plik „helloworld.c” w folderze „src” Axis_2_PWM_SDK, gdzie „helloworld.c” jest głównym plikiem.

Krok 12: Budowanie modułu PWM - przegląd Eksploratora projektów (I)

Sprawdźmy niektóre pliki w Eksploratorze projektów. Najpierw w folderze „design_1_wrapper_hw_platform_0” otwórz „system.hdf”. Ten plik przedstawia mapę adresów dla procesora ps7_cortex9 oraz bloki IP obecne w naszym projekcie.

Krok 13: Budowanie modułu PWM - przegląd Eksploratora projektów (II)

Następnie sprawdź plik „include” i „libsrc” w folderze „Axis_2_PWM_SDK_bsp”. Pliki biblioteczne tutaj umożliwiają nam interakcję ze sprzętowymi urządzeniami peryferyjnymi bez „odtwarzania” rejestrów.

Krok 14: Budowanie modułu PWM - przegląd Eksploratora Projektu (III)

W dokumentacji BSP xtmrctr.h można znaleźć jako bibliotekę Xilinx Timer Control związaną z AXI Timer. Zazwyczaj możemy znaleźć tutaj pożądaną funkcję PWM. Jeśli jednak przeczytasz dokumentację „tmrctr_v4_3”, to pokazuje, że sterownik obecnie nie obsługuje operacji PWM urządzenia. Ze względu na brak funkcji PWM, musimy zamknąć naszą funkcję PWM za pomocą xtmrctr.h i AXI Timer v2.0 Przewodnik po produkcie LogiCORE IP.

Krok 15: Budowanie modułu PWM - funkcja podsumowania PWM (I)

Wracając do głównego pliku „helloworld.c”, dołącz następujące pliki nagłówkowe:

Krok 16: Budowanie modułu PWM - funkcja podsumowania PWM (II)

Zdefiniuj adresy bazowe dwóch AXI TIMER za pomocą „xparameters.h”.

Krok 17: Budowanie modułu PWM - funkcja podsumowania PWM (III)

Zbuduj pożądaną funkcję PWM.

Duty_val: konwertuje wartość stopnia na współczynnik wypełnienia. PWM_Freq_Duty: ustawia żądaną częstotliwość i współczynnik wypełnienia, aby wygenerować PWM. Należy również przypisać okres zegara.

PWM_START: przypisz adres rejestru PWM i rozpocznij generowanie PWM.

PWM_STOP: przypisz adres rejestru PWM i zatrzymaj generowanie PWM.

Reszta kodu demonstracyjnego jest pokazana w „helloworld.c” pod „Axis_2_PWM_SDK”

Krok 18: Budowanie modułu PWM - spraw, aby działał

1. Zaprogramuj FPGA przez SDK

- Podłącz Zybo Board przez port USB do komputera.

- Narzędzia Xilinx -> Program FPGA

2. Uruchom program

Kliknij ikonę „Uruchom” i rozwiń menu -> Uruchom jako -> Uruchom na sprzęcie

3. Terminal SDK

- Otwórz terminal SDK -> Połącz z portem szeregowym -> OK

- Uruchom program. Jeśli kod demonstracyjny zostanie uruchomiony pomyślnie, powinieneś zobaczyć „Inicjalizacja zakończona!” w terminalu SDK.

Krok 19: Strumieniowe przetwarzanie wideo na Digilent ZYBO z OV7670

Załączony kompletny plik archiwum.

Krok 20: Kompletny schemat blokowy

To pokazuje kompletny schemat wszystkich połączeń i bloków IP w projekcie

Krok 21: Podłącz OV7670 do ZYBO

Utwórz połączenie, aby podłączyć moduł ov7670 do ZYBO Pmods

Dane Pmod to Pmod D

Sterowanie Pmod to Pmod C

Dodatkowo podłącz PmodCON3 i serwa zgodnie z opisem w pierwszej połowie tego samouczka

Krok 22: Utwórz projekt bloku

W Flow Navigator kliknij „Create Block Design”, a następnie naciśnij OK.

Krok 23: Dodaj pliki VHDL do sterowania i przechwytywania kamery OV7670

Dodaj pliki VHDL dołączone do tego kroku do projektu

Krok 24: Dodaj plik ograniczeń

Dodaj załączony plik wiązań do swojego projektu.

Krok 25: Dodaj repozytorium IP dla HLS IP

Weź załączony plik Zip i rozpakuj go do nowego folderu o podobnej nazwie w nowym katalogu (folderze) o nazwie „HLS_repo”.

Dodaj repozytorium IP do swojego projektu, przechodząc do katalogu IP i klikając prawym przyciskiem myszy „Dodaj repozytorium…”

Przejdź do katalogu „HLS_repo” i wybierz go.

Opcjonalnie: stwórz blok przetwarzania wideo HLS dla siebie!

Krok 26: Dodaj moduły i adres IP

Dodaj moduły ov7670_axi_stream_capture, debounce i ov7670_controller do schematu blokowego, klikając prawym przyciskiem myszy tło i wybierając „Dodaj moduł…”

Podobnie dodaj adresy IP:

- HLS_Video_Track

- Zapis do bufora klatek wideo

- Odczyt bufora klatek wideo

- Kontroler synchronizacji wideo

- AXI4-Stream do wyjścia wideo

- 3 "Kawałek"

- Stały

- 2 timera AXI

Krok 27: Ustawienia konfiguracji IP

Jak pokazano na zdjęciach

Krok 28: Dodaj i skonfiguruj blokadę IP PS

Dodaj system przetwarzania ZYNQ7 do schematu blokowego

edytuj konfigurację:

-

Konfiguracja PS-PL

-

HP

- Włącz S HP 0

- Włącz S HP 1

-

- Konfiguracja zegara

-

PL Tkaniny Zegary

- FCLK_0 przy 100 MHz

- FCLK_1 przy 25 MHz (zegar wyjściowy)

- FLCK_2 przy 35 MHz (<= 50 MHz) (CameraClock)

-

Krok 29: Część 1. Budowa modułu PWM dla serwomotorów

Wyprowadź axi_timer_0 pwm0 do nowego portu wyjściowego pwm_Xaxis

Przenieś axi_timer_1 pwm0 do nowego portu wyjściowego pwm_Zaxis

Krok 30: Połączenia po stronie wejścia wideo (podświetlony aklk)

Podłącz prawidłowo bloki IP po stronie wejścia wideo

(* te połączenia powinny być utworzone poprzez wybranie odpowiednich opcji podczas automatyzacji połączeń)"aclk" z axi_stream_capture trafia do:

- ap_clk przy zapisie do bufora klatek wideo

- ap_clk na bloku przetwarzania strumienia wideo HLS

- *Alk na AXI smartconnect IP z bufora ramki wideo Zapis do S_AXI_HP0

- *alk odpowiadający kanałom AXI Interconnect IP dla kanałów S_AXI bloku przetwarzania wideo HLS i bufora ramki wideo zapisz S_AXI_HP0_ACLK w bloku PS

Sygnał strumienia wideo jest po prostu połączony szeregowo z bloku przechwytywania do interfejsu pamięci Zynq.

- Wideo przechodzi z bloku przechwytywania do bloku przetwarzania HLS.

- Przetworzone wideo z bloku HLS trafia do bloku zapisu bufora ramki.

- *Blok zapisu do bufora ramki łączy się z interfejsem HP0 w bloku Zynq PS.

- Sygnał m_axis_tuser z wyjścia bloku przechwytywania jest ręcznie podłączany zarówno do sygnału wejściowego video_in_TUSER w bloku przetwarzania HLS, jak i sygnału ap_start w tym samym bloku.

Sygnał TUSER(tuser) jest używany przez protokół strumienia wideo AXI do wskazania początku klatki wideo. AP_Start mówi blokowi HLS, aby rozpoczął przetwarzanie. W ten sposób używamy tusera do wyzwalania bloku HLS w celu przetworzenia każdej klatki tak, jak jest W przypadku podłączania pojedynczego sygnału magistrali i rozdzielania go w ten sposób konieczne jest również podłączenie go do normalnego punktu końcowego reszty magistrali. Vivado zakłada, że jeśli ręcznie podłączasz sygnał, który chcesz odłączyć od tego, z czym normalnie by się łączył.

Ustawienia konfiguracyjne bloków IP:

Zapis do bufora klatek wideo:

Formaty wideo: RGB8

1 próbka na zegar Maks. kolumny: 1280 (>=640) Maks. wiersze: 960 (>=480) Maks. szerokość danych: 8

Krok 31: Połączenia z OV7670

W bloku ov7670_axi_stream_capture

- Uczyń wszystkie wejścia zewnętrznymi (kliknij prawym przyciskiem na pinezkę i wybierz z menu lub lewym przyciskiem myszy->ctrl+T)

- Zostaw imiona takie, jakie są

Na bloku ov7670_controller

- Uczyń wszystkie wyjścia blokowe zewnętrznymi

- Zmień nazwę portu config_finished na led0

- podłącz clk do CameraClock (<=50MHz) (FCLK_2)

Na bloku odbicia

- podłącz wejście button1 do zewnętrznego portu wejściowego o nazwie btn0

- podłącz out1 do linii ponownego wysyłania na bloku IP kontrolera ov7670_controller

- podłącz wejście button2 do zewnętrznego portu wejściowego o nazwie btn3

- podłącz out2n do wejścia ext_reset_in na IP resetowania systemu procesora dla domeny zegara przechwytywania wideo. (*Może być to konieczne po wygenerowaniu tego adresu IP*)

- podłącz clk do CameraClock (<=50MHz) (FCLK_2)

Krok 32: Połączenia po stronie wyjścia wideo

Połączenia dla bloków Video Timing Controller (VTC), AXI4-Stream do Video Out i plasterków

- Użyj zegara 25 MHz (FCLK_1) dla vid_io_out_clk i VTC clk

- Użyj zegara 100 MHz (FCLK_0) do alk na AXI4-Stream do wyjścia wideo

- vtiming_out do vtiming_in

- Odczyt z bufora klatek wideo m_axis_video przechodzi do strumienia AXI4 do wyjścia wideo video_in

- vtg_ce idzie do gen_clken

- Powiąż VTC clken, aclken, vid_io_out_ce ze stałym dout[0:0]

- Przenieś vid_hsync i vid_vsync na zewnętrzne porty wyjściowe odpowiednio vga_hs i vga_vs. (nie na zdjęciu)

Plastry:

-

Plastry powinny być ustawione tak, jak pokazano na załączonych zdjęciach

- zmień nazwy bloków na slice_red, slice_green i slice_blue

- Ustaw zakresy plasterków, jak pokazano na obrazach według nazwy bloku

- podłącz każde wyjście plasterka do wyjścia portu zewnętrznego, jak pokazano na rysunku.

- vid_data[23:0] łączy się z wejściami dla każdego wycinka (Din[23:0])

Krok 33: Uruchom automatyzację blokowania i połączeń

Uruchom Block Automation, aby połączyć elementy z bloku ZYNQ7 PS. Jak pokazano na zdjęciu.

Uruchom automatyzację połączeń, aby utworzyć wszystkie adresy IP połączeń. Zwróć szczególną uwagę na wszystkie opcje na każdym zdjęciu.

W bloku debounce podłącz out2n do wejścia zegara przechwytywania wideo Procesor System Reset ext_reset_in wejście.

Krok 34: Wygeneruj opakowanie HDL

Wygeneruj HDL Wrapper dla swojego projektu bloku.

Ustaw go jako górny moduł.

Krok 35: Wygeneruj strumień bitów, wyeksportuj sprzęt do SDK, uruchom SDK z Vivado

Pamiętaj, aby w eksporcie uwzględnić strumień bitów.

Generowanie strumienia bitów może zająć bardzo dużo czasu.

Następnie uruchom SDK

Krok 36: SDK (bez FreeRTOS)

Ta wersja robi wszystko bez użycia FreeRTOS, ładnie kondensując kod.

Utwórz samodzielny BSP na podstawie projektu sprzętu. Domyślne opcje powinny być w porządku. Upewnij się, że źródła BSP zostały wygenerowane.

Utwórz aplikację, jak pokazano na obrazku. (pusta aplikacja)

Usuń automatycznie wygenerowany plik główny i zaimportuj dołączone pliki.

Krok 37: Wdrożenie FreeRTOS

Ta wersja używa FreeRTOS. Utwórz FreeRTOS901 BSP na podstawie projektu sprzętu. Domyślne opcje powinny być w porządku. Upewnij się, że źródła BSP zostały wygenerowane.

Utwórz aplikację, jak pokazano na obrazku. (pusta aplikacja)

Usuń automatycznie wygenerowany plik główny i zaimportuj dołączone pliki.

Krok 38: Instrukcja użytkowania

Ten projekt jest trochę trudny do uruchomienia. Postępuj zgodnie z instrukcjami w kolejności.

Upewnij się, że ZYBO niczego nie ładuje się samoczynnie po włączeniu. Oznacza to, że dioda Gotowe nie powinna się świecić. Jednym ze sposobów, aby to zrobić, jest ustawienie zworki źródła rozruchowego na JTAG.

Otwórz projekt (FreeRTOS lub nie), który chcesz zaprogramować z SDK

- Włącz ZYBO. Dioda Gotowe nie powinna się świecić.

- Zaprogramuj FPGA za pomocą pliku bitowego. Dioda Gotowe powinna się zaświecić. Led0 nie powinien się świecić.

- Uruchom kod (pamiętaj, aby przejść poza początkowy punkt przerwania, jeśli to robisz).

W tym momencie powinieneś uzyskać wyjście na swoim wyświetlaczu VGA.

Aby ponownie uruchomić (jeśli jest to błąd lub cokolwiek innego): szybko naciśnij przycisk PS-SRST lub wyłącz ZYBO, a następnie włącz ponownie. Kontynuuj od kroku 2.

Zatrzymanie procesora z debuggerem spowoduje, że kamera zatrzyma się w pozycji zamiast poruszać się. Strumień wideo i tak będzie kontynuowany.

Krok 39: Odniesienia i linki

Przewodniki i dokumentacja Xilinx:

- PG044 - AXI-Stream do wyjścia wideo

- PG278 - Odczyt/zapis bufora ramek wideo

Inne linki:

- Blog Lauriego - wejście VDMA

- Blog Lauriego - wyjście OV7670 na VGA przy użyciu BRAM

- Wiki Hamsterworks, autorstwa Mike'a Fieldsa, oryginalnego źródła kodu OV7670

- Karta katalogowa przedstawiająca podstawowe specyfikacje czasowe

Zalecana:

Przełącznik pochylenia z metalową kulką SW-520D z czujnikiem wibracji - Visuino: 6 kroków

Przełącznik pochylenia z metalową kulką SW-520D z czujnikiem wibracji - Visuino: Ten podstawowy przełącznik pochylenia SW-520D może być z łatwością używany do wykrywania orientacji. Wewnątrz puszki znajduje się kulka, która styka się z kołkami, gdy skrzynka jest w pozycji pionowej. Przechyl obudowę, a kulki się nie zetkną, nie nawiązując w ten sposób połączenia.Czujnik przechy

Robot Arduino z odległością, kierunkiem i stopniem obrotu (wschód, zachód, północ, południe) sterowany głosem za pomocą modułu Bluetooth i autonomicznego ruchu robota.: 6 kroków

Robot Arduino z odległością, kierunkiem i stopniem obrotu (wschód, zachód, północ, południe) sterowany głosem za pomocą modułu Bluetooth i autonomicznego ruchu robota.: Ta instrukcja wyjaśnia, jak zrobić robota Arduino, który można przesuwać w wymaganym kierunku (do przodu, do tyłu , Lewo, Prawo, Wschód, Zachód, Północ, Południe) wymagana odległość w centymetrach za pomocą polecenia głosowego. Robot może być również poruszany autonomicznie

Jak zmodyfikować mikro serwomotor (SG90) do ciągłego obrotu: 6 kroków (ze zdjęciami)

Jak zmodyfikować mikro serwomotor (SG90) do ciągłego obrotu: O nie! Skończyły mi się silniki prądu stałego! Czy masz jakieś zapasowe serwa i rezystory siedzące dookoła? W takim razie zmodyfikujmy to! Normalne serwo obraca się o około 180 stopni. Oczywiście nie możemy go używać do pojazdu jeżdżącego na kołach. W tym samouczku będę goi

5-centowy czujnik pochylenia: 4 kroki (ze zdjęciami)

Czujnik przechyłu za pięć centów: jest to podstawowy czujnik przechyłu inspirowany czujnikami w stylu kuli i klatki, ale 2d zamiast 3d. Przechwycone nickle łączy pary przewodów w zależności od orientacji czujnika. Są szybkie w budowie i dość tanie; Wymyśliłem je do projektu z

Obiektyw aparatu DSLR z przesunięciem pochylenia: 6 kroków

Obiektyw aparatu DSLR z przesunięciem pochylenia: Czego będziesz potrzebować: 1) Korpus lustrzanki lub lustrzanki cyfrowej z wymiennym obiektywem. 2) Powiększony obiektyw. Ebay jest świetnym źródłem informacji, możesz wybrać wysokiej jakości obiektyw za około 15,3 USD) Gumowy tłok w kształcie akordeonu (najlepiej czarny, aby zapobiec