Spisu treści:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:30.

- Ostatnio zmodyfikowany 2025-01-23 15:03.

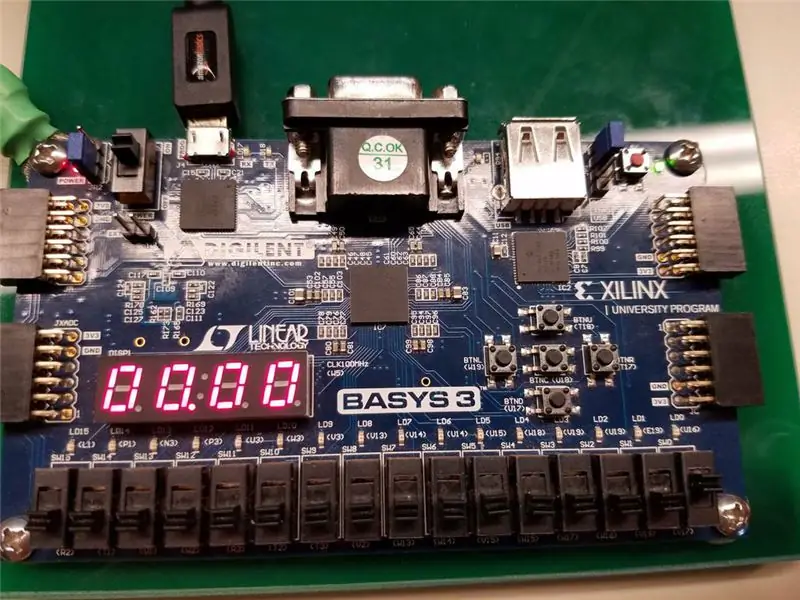

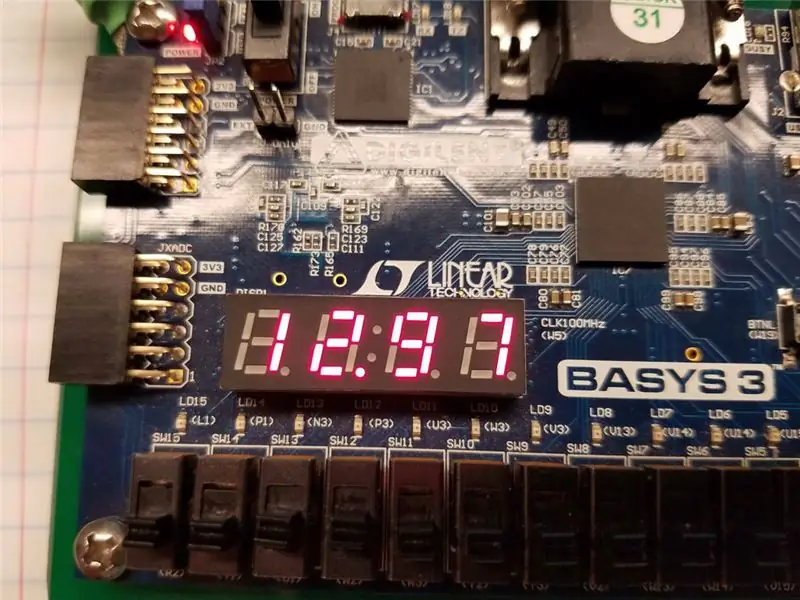

Witamy w instrukcji, jak zbudować stoper przy użyciu podstawowej płytki VHDL i Basys 3. Cieszymy się, że możemy podzielić się z Tobą naszym projektem! To był ostatni projekt kursu CPE 133 (Digital Design) w Cal Poly, SLO jesienią 2016. Zbudowany przez nas projekt to prosty stoper, który uruchamia, resetuje i zatrzymuje czas. Jako wejścia przyjmuje trzy przyciski na płycie Basys3, a czas jest wyświetlany na czterocyfrowym siedmiosegmentowym wyświetlaczu płyty. Upływający czas jest wyświetlany w formacie sekund: centysekund. Wykorzystuje zegar systemowy płyty jako wejście do śledzenia upływu czasu i wyświetla czas w postaci czterech cyfr na siedmiosegmentowym wyświetlaczu.

Krok 1: Materiały

Materiały, których będziesz potrzebować do tego projektu:

- 1 komputer z zainstalowanym pakietem Vivado Design Suite WebPack firmy Xilinx (preferowana wersja 2016.2)

- 1 karta FPGA Digilent Basys3 Xilinx Artix-7

- 1 kabel portu USB

Krok 2: Ustawianie wejść i wyjść

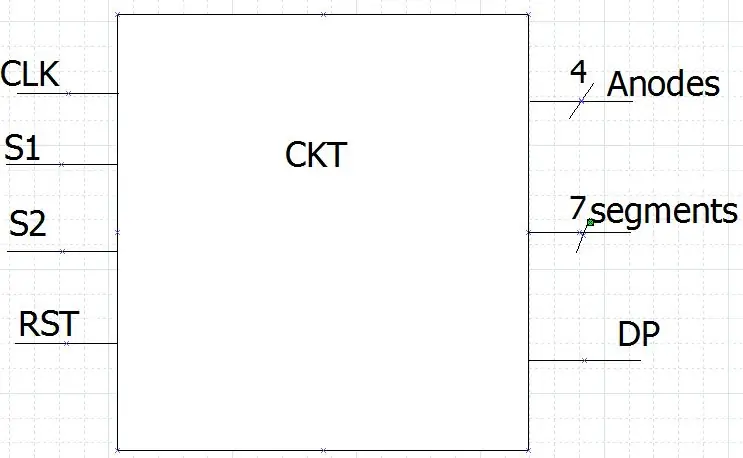

Powyższy rysunek przedstawia schemat blokowy najwyższego poziomu głównego modułu stopera. Stoper przyjmuje wejścia „CLK” (zegar), „S1” (przycisk start), „S2” (przycisk pauzy) i „RST” (reset) oraz posiada 4-bitowe wyjście „Anody”, 7-bitowe wyjście „segment” i jednobitowe wyjście „DP” (przecinek dziesiętny). Gdy wejście „S1” jest w stanie wysokim, stoper rozpoczyna odliczanie czasu. Gdy „S2” jest niskie, stoper zatrzymuje czas. Gdy „RST” jest wysokie, stoper zatrzymuje się i resetuje czas. W obwodzie znajdują się cztery podmoduły: dzielnik zegara, licznik cyfr, sterownik wyświetlacza siedmiosegmentowego i koder wyświetlacza siedmiosegmentowego. Główny moduł stopera łączy wszystkie podmoduły ze sobą oraz z wejściami i wyjściami.

Krok 3: Tworzenie zegarów

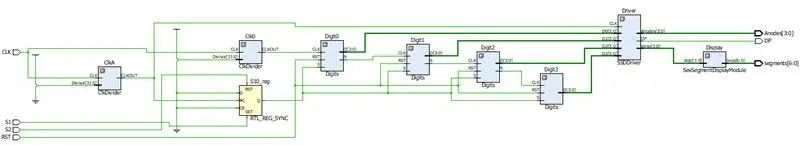

Moduł dzielnika zegara pobiera zegar systemowy i wykorzystuje wejście dzielnika do utworzenia zegara o dowolnej prędkości nie większej niż zegar systemowy. Stoper wykorzystuje dwa różne moduły zegarowe, jeden, który tworzy zegar 500 Hz, a drugi, który tworzy zegar 100 Hz. Schemat dzielnika zegara pokazano na powyższym rysunku. Dzielnik zegara przyjmuje jednobitowe wejście „CLK”, 32-bitowe wejście „Divisor” i jednobitowe wyjście „CLKOUT”. „CLK” to zegar systemowy, a „CLKOUT” to zegar wynikowy. Moduł zawiera również bramkę NOT, która przełącza sygnał „CLKTOG”, gdy licznik osiągnie wartość dzielnika.

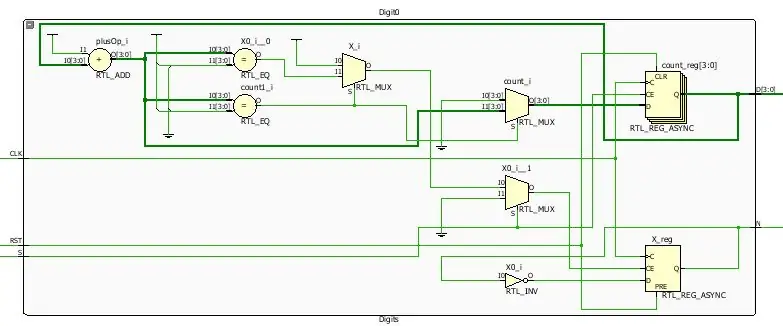

Krok 4: Liczenie do dziesięciu

Licznik cyfr zlicza każdą cyfrę od 0 do 10 i tworzy kolejny zegar dla następnej cyfry, która oscyluje, gdy liczba osiągnie 10. Moduł przyjmuje 3 wejścia jednobitowe „S”, „RST” i „CLK” i daje jednobitowe wyjście „N” i 4-bitowe wyjście „D”. Wejście „S” to zezwolenie na wejściu. Zegar włącza się, gdy „S” jest wysokie i wyłącza, gdy „S” jest niskie. „RST” to wejście resetujące, więc zegar resetuje się, gdy „RST” jest wysoki. „CLK” to wejście zegara dla licznika cyfr. „N” to wyjście zegara, które staje się zegarem wejściowym dla następnej cyfry. Wyjście „D” przedstawia binarną wartość cyfry, na której znajduje się licznik.

Krok 5: Wyświetlanie liczb

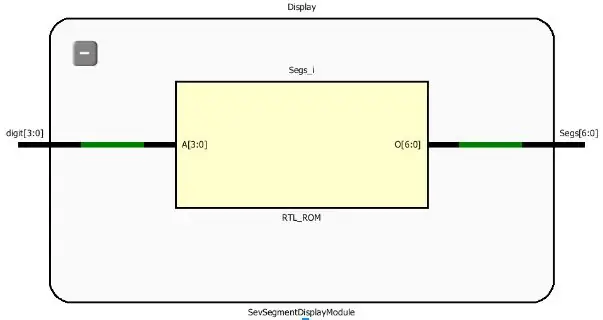

Koder wyświetlacza siedmiosegmentowego zakoduje liczbę binarną otrzymaną z modułu sterownika wyświetlacza siedmiosegmentowego i zamieni ją w strumień bitów, które będą interpretowane jako wartości „1” lub „0” dla każdego segmentu wyświetlacza. Liczba binarna jest odbierana przez moduł jako 4-bitowa „cyfra” wejścia i powoduje powstanie 7-bitowych „segmentów” wyjścia. Moduł składa się z pojedynczego bloku przetwarzania przypadku, który przypisuje określony 7-bitowy strumień dla każdej możliwej wartości wejściowej od 0 do 9. Każdy bit w siedmiobitowych strumieniach reprezentuje jeden z siedmiu segmentów cyfr na wyświetlaczu. Kolejność segmentów w strumieniu to „abcdefg”, gdzie „0” oznaczają segmenty, które zapalają się dla podanej liczby.

Krok 6: Jak wyświetlić stoper

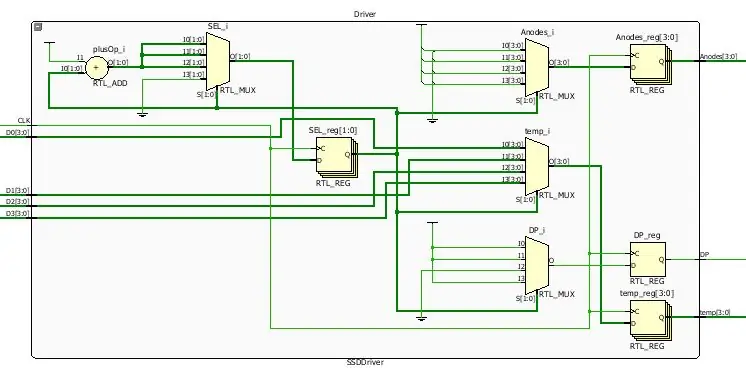

W siedmiosegmentowym module sterownika wyświetlacza znajdują się cztery 4-bitowe wejścia „D0”, „D1”, „D2” i „D3”, z których każde reprezentuje cztery wyświetlane cyfry. Wejście „CLK” to wejście zegara systemu. Wyjście jednobitowe „DP” przedstawia kropkę dziesiętną na wyświetlaczu siedmiosegmentowym. 4-bitowe wyjście „Anody” określa, która cyfra na siedmiosegmentowym wyświetlaczu jest pokazywana, a 4-bitowe wyjście „temp” zależy od stanu 2-bitowego wejścia sterującego „SEL”. Moduł wykorzystuje 4 multipleksery dla wejścia sterującego „SEL” i trzech wyjść; „Anody”, „temp” i „DP”.

Krok 7: Połącz wszystko razem

Do utworzenia przycisków startu i pauzy używany jest blok procesowy 'if' działający w oparciu o zegar 500Hz. Następnie połącz wszystkie submoduły razem w głównym module stopera, deklarując składowe każdego submodułu i używając różnych sygnałów. Cyfrowe podmoduły przejmują wyjście zegara poprzedniego podmodułu cyfrowego, przy czym pierwszy z nich przyjmuje zegar 100Hz. Wyjścia „D” podmodułów cyfrowych stają się następnie wejściami „D” modułu sterownika wyświetlacza siedmiosegmentowego. I wreszcie, wyjście „temp” modułu sterownika wyświetlacza siedmiosegmentowego staje się wejściem „temp” siedmiosegmentowego modułu enkodera.

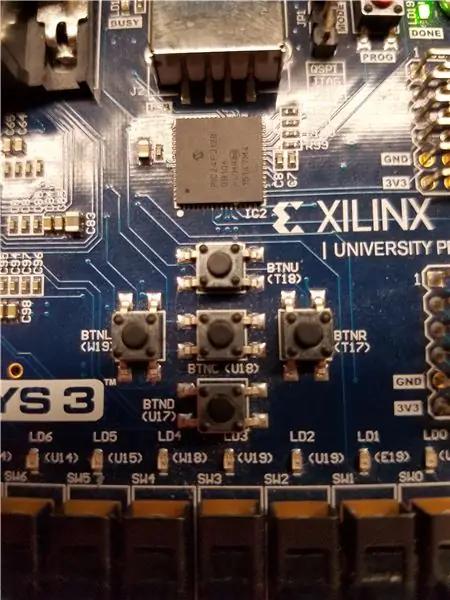

Krok 8: Ograniczenia

Użyj 3 przycisków (W19, T17 i U18) dla wejść "RST", "S1" i "S2". W19 to przycisk resetowania, T17 to przycisk start (S1), a U18 to przycisk pauzy (S2). Wymagane jest również ograniczenie wejścia zegara przy użyciu portu W5. Pamiętaj też, aby dodać tę linię do ograniczenia zegara:

create_clock -add -name sys_clk_pin -okres 10.00 -przebieg {0 5} [get_ports {CLK}]

Połącz również anody i segmenty z płytką, aby stoper był wyświetlany na wyświetlaczu siedmiosegmentowym, jak widać w pliku ograniczeń.

Krok 9: Testowanie

Upewnij się, że Twoje urządzenie działa, bawiąc się trzema przyciskami: naciskając i przytrzymując je w każdej możliwej kolejności, aby znaleźć ewentualne problemy z kodem.

Zalecana:

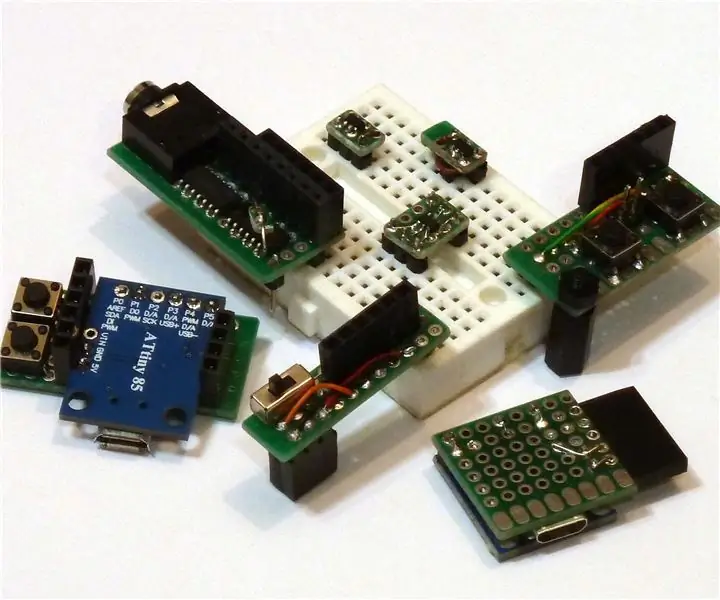

Płyta perforowana Clean-Cut FR4 (płyta prototypowa/prototypowa): 10 kroków (ze zdjęciami)

Płytka perforowana Clean-Cut FR4 (płyta prototypowa/prototypowa): (tl; dr: nożyce lotnicze i kamień karborundowy pod wodą) W miarę jak wkraczamy w trzecią dekadę XXI wieku, bardzo wysokiej jakości niestandardowe płytki drukowane można zamówić w bardzo małe ilości za bardzo niskie koszty… jeśli nie masz nic przeciwko czekaniu

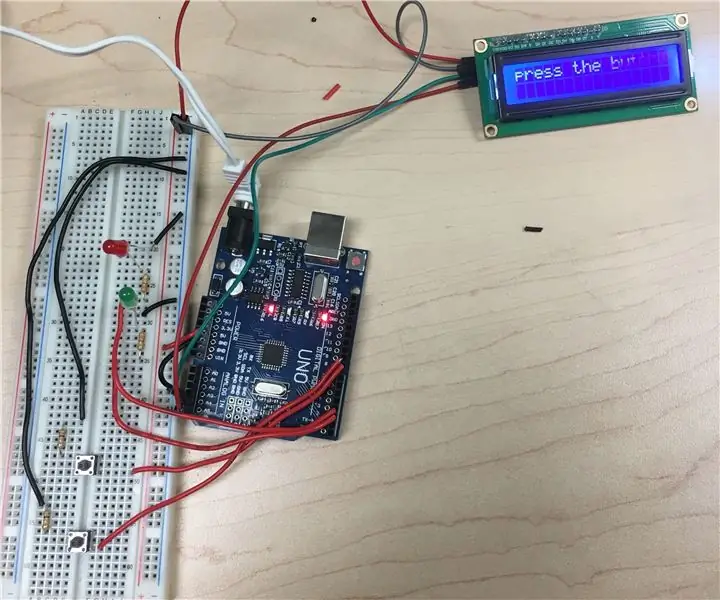

Stoper Arduino z wyświetlaczem LCD I2C: 5 kroków

Stoper Arduino przy użyciu I2C LCD: W tym projekcie nauczę Cię używać wyświetlacza LCD i Arduino jako interaktywnego stopera. Gdy Twój projekt zostanie ukończony z dostarczonym kodem, powinien wyglądać jak na powyższym zdjęciu.Przejdź do następnego kroku, aby dowiedzieć się, od czego zacząć

VHDL Basys3: Connect 4 Gra: 5 kroków

VHDL Basys3: Gra Connect 4: Wprowadzenie: Jest to cyfrowa gra logiczna Connect 4 zaprojektowana w VHDL przy użyciu oprogramowania Vivado i zaprogramowana na płycie Basys3. Konstrukcja i projekt tego projektu są pośrednie, ale nowicjusze mogą skopiować kroki i zbudować cyfrową ga

Jednominutowy stoper VHDL: 5 kroków

Stoper jednominutowy VHDL: To jest samouczek, jak zbudować jednominutowy stoper przy użyciu VHDL i płyty Basys 3. Takie urządzenie jest idealne do gier, w których każdy gracz ma maksymalnie minutę na wykonanie ruchu. Stoper dokładnie wyświetla sekundy i milisekundy o

Stoper VHDL: 8 kroków (ze zdjęciami)

Stoper VHDL: To jest samouczek na temat tworzenia stopera przy użyciu VHDL i płytki FPGA, takiej jak płytka Basys3 Atrix-7. Stoper może liczyć od 00.00 sekund do 99,99 sekund. Wykorzystuje dwa przyciski, jeden do przycisku start/stop, a drugi do