Spisu treści:

- Krok 1: Konfiguracja projektu w Vivado dla Ernie

- Krok 2: Tworzenie PWM Erniego w Vivado

- Krok 3: Tworzenie TDOA Erniego w Vivado

- Krok 4: Pakowanie i eksportowanie Ernie

- Krok 5: Budowanie Ernie

- Krok 6: Pierwsze BSP Ernie

- Krok 7: FreeRTOS za Ernie

- Krok 8: Importowanie kodu C Erniego

- Krok 9: Debugowanie Ernie

- Krok 10: Uczynienie Ernie Autonomous

- Krok 11: Sprawienie, by Ernie był słodki

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:28.

- Ostatnio zmodyfikowany 2025-01-23 15:02.

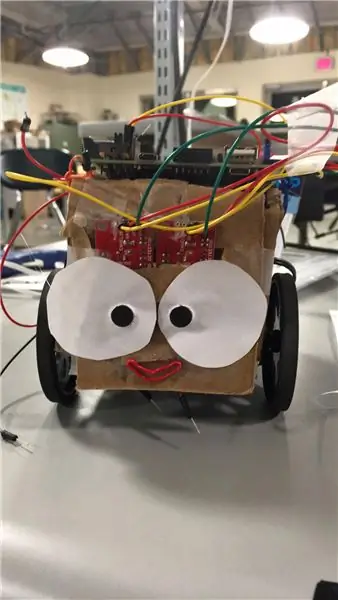

To jest samouczek, jak zbudować Ernie, autonomicznego robota podążającego za dźwiękiem, używając tablicy Zybo. Omówiono w nim, jak: stworzyć projekt w Vivado, stworzyć serwonapędy przypominające PWM w FPGA, połączyć się z dwoma czujnikami dźwięku, stworzyć różnicę czasu przybycia IP, użyć freeRTOS i uruchomić zybo z akumulatora. To był nasz ostatni projekt dla klasy systemów operacyjnych czasu rzeczywistego (CPE 439) w Cal Poly SLO.

Lista wyposażenia:

- 1 - Płytka rozwojowa ZYBO Zynq 7000

- 2 - Serwomechanizm ciągłego obrotu paralaksy

- 2 - Czujnik dźwięku (wykrywacz dźwięku SparkFun)

- Akumulator litowo-jonowy 1 - 5 V USB (do płyty)

- 4 - baterie AA (do serw)

- 1 - zestaw baterii AA (z 4 gniazdami baterii)

- 1 - Kabel Micro USB

- 1 - Deska do krojenia chleba

- wiele - przewody męskie na męskie

- 1 - Serwo podwozie

Wymagania Systemowe:

- Xilinx Vivado Design Suite 2016.2

- Pilny Adept 2.16.1

Krok 1: Konfiguracja projektu w Vivado dla Ernie

- Pojawi się kreator

- Kliknij Następny

-

Następnie nazwij projekt

- Nigdy nie używaj nazwy projektu lub ścieżki do katalogu, która zawiera spacje!!!!!

- To będzie projekt RTL.

- Nie chcemy podawać źródeł

-

Klikając Dalej, przechodzimy do strony części. Używamy ZYNQ XC7Z010-1CLG400C.

- Vivado nie ma Zybo wymienionego jako jedna z predefiniowanych płyt. Wybierz: „części”, a następnie wyszukaj xc7z010clg400-1.

- Jeśli przez pomyłkę wybierzesz niewłaściwą część, możesz łatwo zmienić układy: Narzędzia -> Ustawienia projektu -> Ogólne i kliknij kropki po prawej stronie „Urządzenie projektu”

-

Kliknij opcję Utwórz projekt blokowy.

Nadaj mu teraz nazwę design_1

- Zobaczysz zielony pasek z napisem Dodaj IP, kliknij go.

-

Szukaj Zynq.

- Kliknij dwukrotnie System przetwarzania ZYNQ7,

- Ten blok pojawi się w naszym projekcie bloku.

- Zobaczysz zielony pasek z napisem Run Block Automation, kliknij go.

- Pobierz zybo_zynq_def.xml poniżej.

-

W Vivado kliknij „Importuj ustawienia XPS” i wybierz „zybo_zynq_def.xml”

To wstępnie wypełnia konfigurację bloku Vivado wszystkimi wbudowanymi urządzeniami peryferyjnymi i przypisaniami pinów płyty Zybo

-

Kliknij dwukrotnie blok ZYNQ.

-

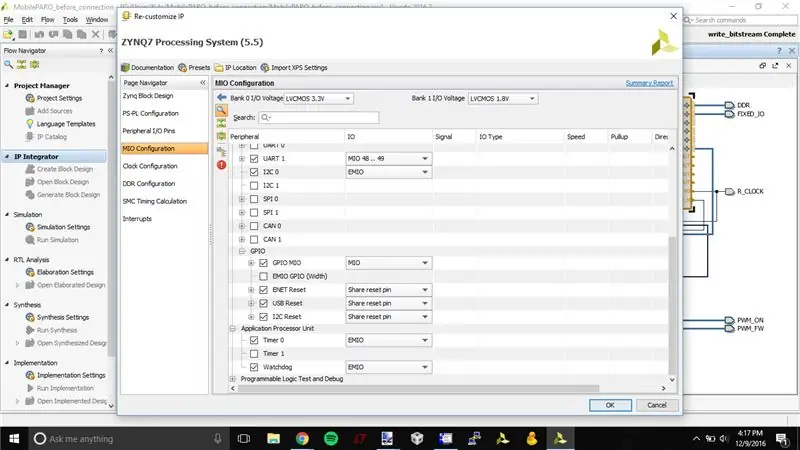

Konfiguracja MIO

- Włącz Timer 0 (pod Jednostka Procesora Aplikacji - img 1)

- Włącz Watchdog (w Application Processor Unit- img 1)

- Włącz GPIO->GPIO MIO (w Application Processor Unit - img 2)

- Włącz GPIO->ENET Reset (pod I/O Peripherals- img 2)

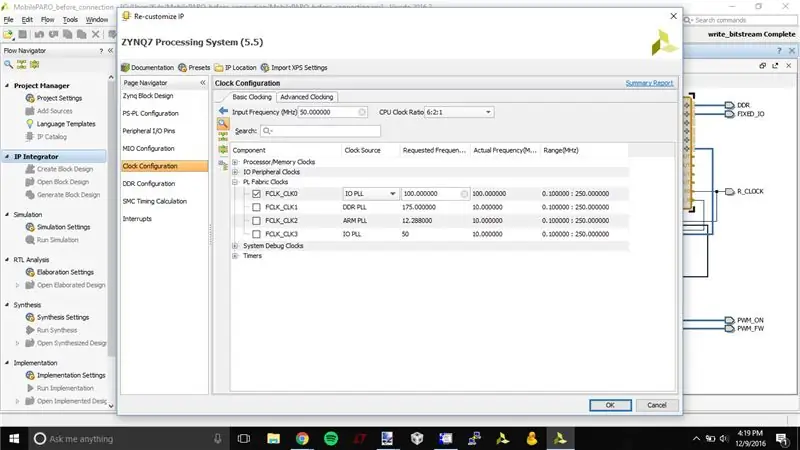

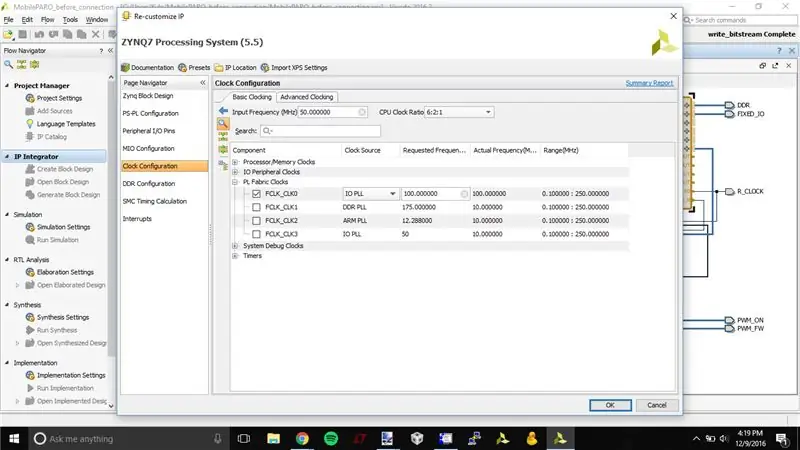

- Konfiguracja zegara

Wyłącz FCLK0 (pod PL Fabric Clocks - img 3)

-

- Kliknij OK.

-

„Uruchom automatyzację bloku” teraz.

Pojawią się pytania dotyczące sygnałów, powiedz OK

-

Kliknij „Generuj opakowanie HDL”.

Będziemy chcieli skopiować wygenerowany wrapper, aby umożliwić edycję użytkownika

- Kliknij OK.

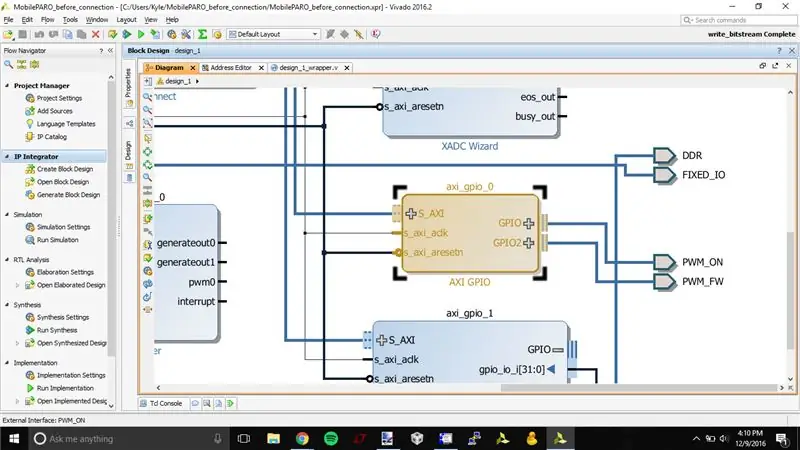

Krok 2: Tworzenie PWM Erniego w Vivado

Ten krok wygeneruje adres IP PWM z danymi wejściowymi przesłanymi przez bibliotekę AXI.

-

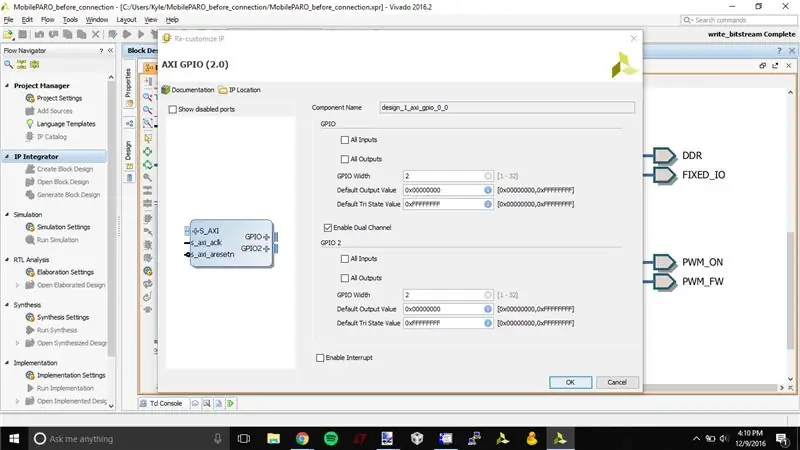

Utwórz blok AXI GPIO, klikając prawym przyciskiem myszy tło i klikając „dodaj IP”

wpisz „AXI_GPIO” w pasku wyszukiwania i wybierz ten pakiet

-

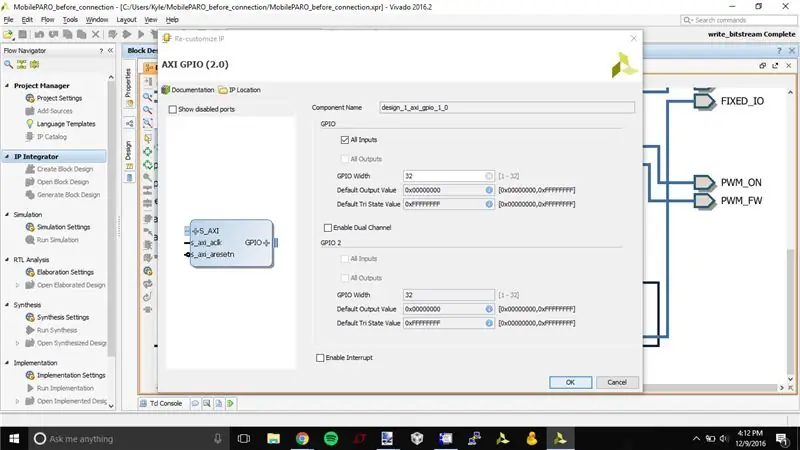

Ponownie dostosuj adres IP, klikając dwukrotnie nowy blok axi_gpio_0

- pod GPIO ustaw szerokość GPIO na 2. Te bity będą sygnałem PWM_ON do sterowania każdą instancją modułu PWM.

- kliknij "włącz podwójny kanał"

- pod GPIO 2 ustaw szerokość GPIO na 2. Te bity będą sygnałem PWM_FW, aby ustawić kierunek każdej instancji modułu PWM.

-

Kliknij prawym przyciskiem myszy port wyjściowy axi_gpio_0 oznaczony GPIO i wybierz „Make External”

- Kliknij nowe wyjście oznaczone GPIO i przejdź do zakładki „właściwości” na lewym pasku narzędzi i zmień nazwę na PWM_ON

- Kliknij nowe wyjście oznaczone GPIO2 i przejdź do zakładki „właściwości” na lewym pasku narzędzi i zmień nazwę na PWM_FW

-

Wybierz opcję Uruchom automatyzację połączeń na zielonym banerze nad schematem blokowym.

Jeśli ręcznie podłączysz porty, adresy AXI mogą nie zostać skonfigurowane, co może spowodować późniejsze problemy z komunikacją

-

W panelu Flow Navigator wybierz Project manager -> Add Sources, aby utworzyć nowy niestandardowy blok IP

- wybierz „dodaj lub utwórz źródła projektu” i naciśnij Dalej

- kliknij „Utwórz plik”, zmień typ pliku na „SystemVerilog” i wpisz „pwm” w polu nazwy pliku, a następnie kliknij OK

- kliknij Zakończ

-

zignoruj okno Define Module, naciskając OK (nadpiszemy je później)

jeśli pojawi się pytanie, czy jesteś pewien, kliknij Tak

-

Na karcie źródeł kliknij dwukrotnie plik pwm.sv (znajdujący się w „Źródła projektu/design_1_wrapper”)

Skopiuj/wklej cały kod SystemVerilog z pliku pwm.txt załączonego poniżej

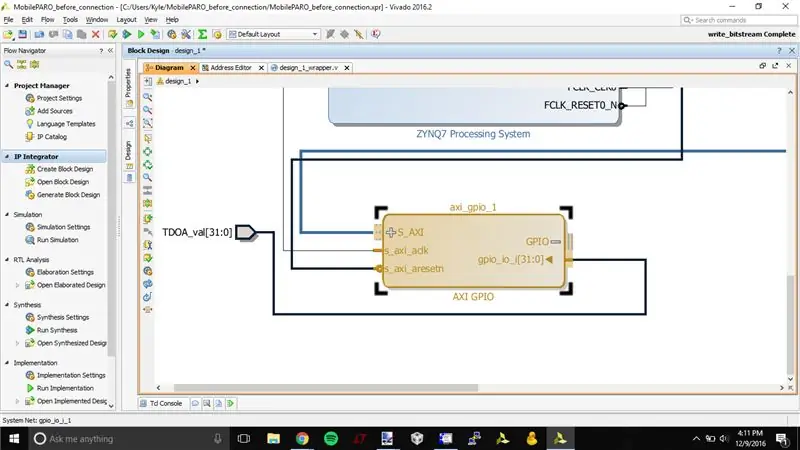

Krok 3: Tworzenie TDOA Erniego w Vivado

Ten krok wygeneruje adres IP TDOA, którego dane wyjściowe można odczytać za pośrednictwem biblioteki AXI

-

Utwórz blok AXI GPIO, klikając prawym przyciskiem myszy tło i klikając „dodaj IP”

wpisz „AXI_GPIO” w pasku wyszukiwania i wybierz ten pakiet

-

Ponownie dostosuj adres IP, klikając dwukrotnie nowy blok axi_gpio_1

- pod GPIO, zaznacz pole "Wszystkie wejścia" i ustaw szerokość GPIO na 32. Ta magistrala będzie różnicą czasu przybycia między dwoma czujnikami.

- wewnątrz bloku axi_gpio_1 kliknij + obok portu GPIO, aby wyświetlić gpio_io_i[31:0].

-

Kliknij prawym przyciskiem myszy port wyjściowy axi_gpio_1 oznaczony jako gpio_io_i[31:0] i wybierz „Utwórz zewnętrzny”

Kliknij nowe wejście oznaczone gpio_io_i[31:0] i przejdź do zakładki „Właściwości” na lewym pasku narzędzi i zmień nazwę na TDOA_val

-

Wybierz opcję Uruchom automatyzację połączeń na zielonym banerze nad schematem blokowym.

Jeśli ręcznie podłączysz porty, adresy AXI mogą nie zostać skonfigurowane, co może spowodować późniejsze problemy z komunikacją

-

W panelu Flow Navigator wybierz Project manager -> Add Sources, aby utworzyć nowy niestandardowy blok IP

- wybierz „dodaj lub utwórz źródła projektu” i naciśnij Dalej

- kliknij „Utwórz plik”, zmień typ pliku na „SystemVerilog” i wpisz „tdoa” w polu nazwy pliku, a następnie kliknij OK

- kliknij Zakończ

-

zignoruj okno Define Module, naciskając OK (nadpiszemy je później)

jeśli pojawi się pytanie, czy jesteś pewien, kliknij Tak

-

Na karcie źródeł kliknij dwukrotnie plik tdoa.sv (znajdujący się w „Źródła projektu/design_1_wrapper”)

Skopiuj/wklej cały kod SystemVerilog z pliku tdoa.txt załączonego poniżej

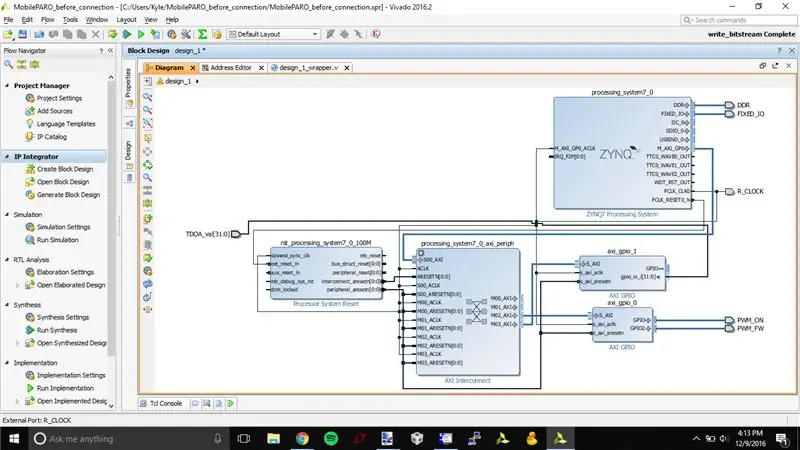

Krok 4: Pakowanie i eksportowanie Ernie

- Sprawdź, czy schemat blokowy wygląda jak załączony zrzut ekranu

-

Na karcie źródeł kliknij prawym przyciskiem myszy design_1.bd i wybierz „Utwórz opakowanie HDL…”

- Wybierz "Kopiuj wygenerowane wyjście, aby umożliwić edycję użytkownika", a następnie naciśnij "OK"

- Skopiuj kod z załączonego poniżej design_1_wrapper.txt i wklej go w miejsce wygenerowanego kodu design_1_wrapper.v

- zapisz design_1_wrapper.v

-

Na karcie źródła kliknij dwukrotnie plik ZYBO_Master.xdc w obszarze Constraints/constrs1

- Skopiuj kod z załączonego poniżej pliku ZYBO_Master.txt i wklej go w miejsce istniejącego kodu ZYBO_Master.xdc

-

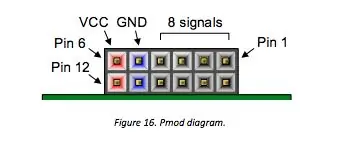

Zwróć uwagę na następujące styki wejścia/wyjścia:

- L15: sygnał PWM dla lewego silnika (Pmod JA2 na Zybo)

- L14: sygnał PWM dla prawego silnika (Pmod JA8 na Zybo)

- V12: wejście bramki z czujnika dźwięku 1 (Pmod JE1 na Zybo)

- K16: wejście bramki z czujnika dźwięku 2 (Pmod JE2 na Zybo)

-

W okienku Flow Navigator kliknij „Generuj strumień bitów” w obszarze Program i debugowanie

jeśli myślisz, że zostało to zrobione od razu, prawdopodobnie tak nie jest. poważnie, zrób trochę herbaty

-

Kliknij Plik->Eksportuj->Generuj sprzęt

Zaznacz „Uwzględnij strumień bitów” i naciśnij OK

- Kliknij Plik-> Uruchom SDK

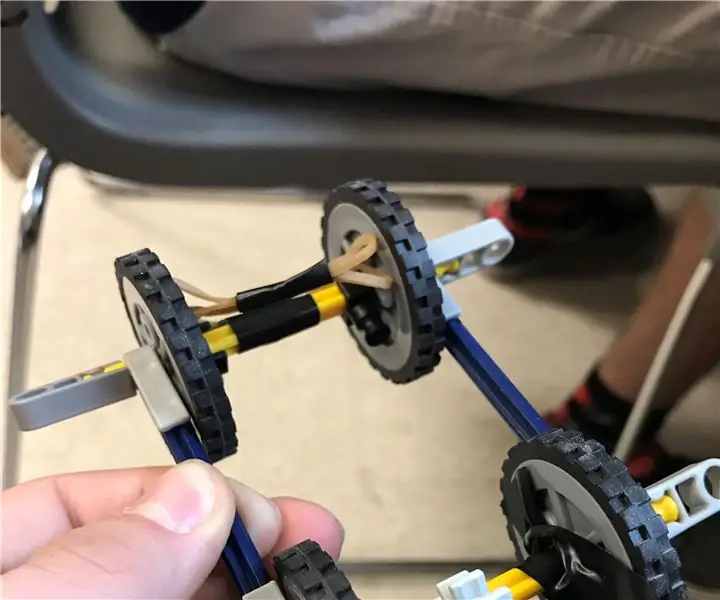

Krok 5: Budowanie Ernie

- Zamontuj serwa do obudowy serwomechanizmu.

-

Postępując zgodnie z arkuszem danych serw, wykonaj następujące czynności:

- podłącz masę serw do pinów uziemienia na JA Pmod Zybo (patrz załączony obraz pinout)

-

podłącz pin zasilania serw do akumulatora AA;

Odkryliśmy, że gdy serwa są podłączone do Vdd Zybo, płyta pobiera zbyt dużo prądu, powodując ciągłe resetowanie się płyty

- podłącz piny sygnału wejściowego do odpowiednich pinów wyjściowych Zybo (lewy: JA2, prawy: JA8)

- zamontuj czujniki dźwięku z przodu obudowy, zwrócone do przodu, trzymając je jak najbliżej siebie

-

użyj przewodnika podłączania czujnika dźwięku, aby zintegrować czujniki dźwięku

- podłącz uziemienie i piny Vdd każdego czujnika dźwięku do masy i pinów Vdd na JE Pmod Zybo (patrz załączony obraz pinout)

- Podłącz sworzeń bramki lewego czujnika dźwięku do JE1;

- Podłącz sworzeń bramki prawego czujnika dźwięku do JE2

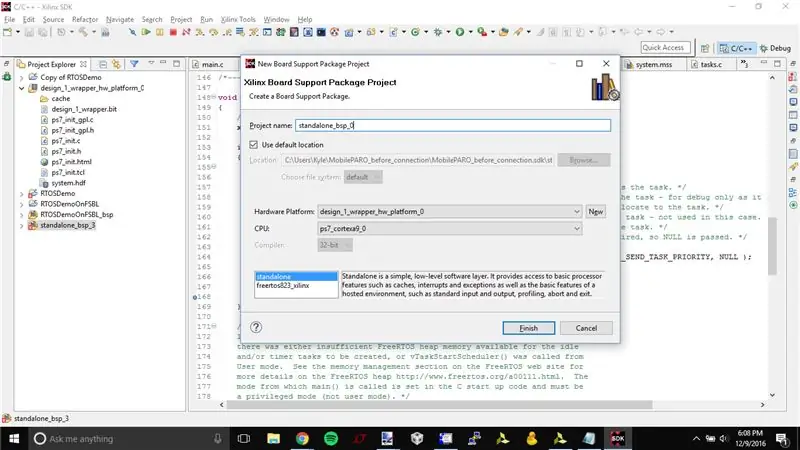

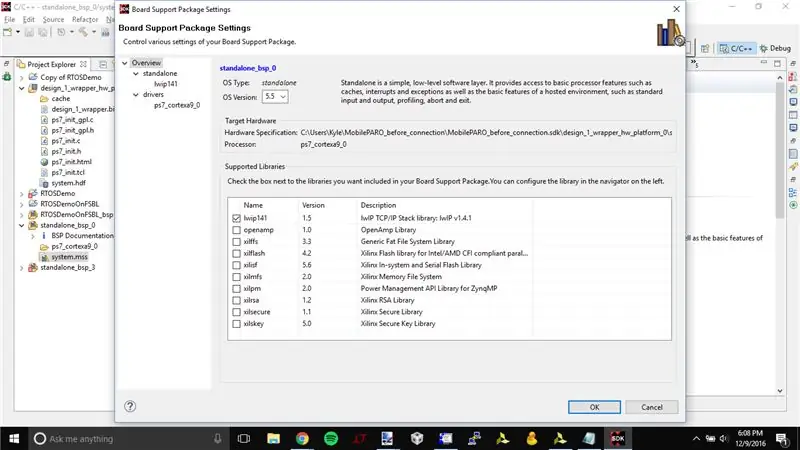

Krok 6: Pierwsze BSP Ernie

-

Utwórz BSP, aby zamknąć platformę, którą właśnie stworzyliśmy.

Możesz to uzyskać poprzez Plik -> Nowy -> Pakiet wsparcia płyty

-

Pojawi się kreator, który pomoże ci stworzyć BSP.

- Chcemy powiązać ten BSP z naszą platformą, którą właśnie stworzyliśmy, więc

- Platforma sprzętowa powinna być zgodna z tą, którą właśnie stworzyliśmy (patrz zdjęcie 1)

- Naszym procesorem będzie procesor _0.

- Kliknij Zakończ

- Upewnij się, że zaznaczyłeś lwip141 do włączenia do twojego bsp w wyskakującym oknie (patrz img 2)

Krok 7: FreeRTOS za Ernie

-

Pobierz najnowszą wersję FreeRTOS z Sourceforge.

Jeśli pobrany plik jest plikiem wykonywalnym, uruchom go, aby wyodrębnić pliki FreeRTOS do katalogu projektu

- Pozostaw ten pakiet SDK otwarty i kliknij Plik -> Importuj.

- Chcemy kliknąć Ogólne -> Z istniejącego obszaru roboczego, a następnie przejść do miejsca, w którym pobraliśmy FreeRTOS.

-

Nasze demo będzie zlokalizowane w FreeRTOS/Demo/CORTEX_A9_Zynq_ZC702. Po wybraniu tego folderu powinniśmy zobaczyć trzy projekty (nasz kod (OS), to BSP i platforma HW).

TYLKO Importuj RTOSDemo do bieżącego obszaru roboczego

-

We wszystkich projektach „niebieskich” folderów zmień BSP, do którego się odwołuje

- Kliknięcie prawym przyciskiem myszy i wybranie opcji „Zmień BSP z odniesieniem”.

- Wybierz BSP, który właśnie utworzyłeś dla swojego Zybo

- Edycja kodu w folderach SDK Blue Xilinx to rzeczywiste projekty kodu.

Krok 8: Importowanie kodu C Erniego

- W katalogu RTOSDemo/src nadpisz istniejący plik main.c załączonym tutaj plikiem main.c.

- Skopiuj plik main_sound.c do katalogu RTOSDemo/src.

Krok 9: Debugowanie Ernie

- Wybierz Uruchom -> Konfiguracje debugowania

- W lewym okienku utwórz nowe uruchomienie Debugera systemu

-

W zakładce Konfiguracja docelowa,

wybierz „Zresetuj cały system”, aby wybrać zarówno to, jak i ps7_init

-

Teraz wybierz zakładkę Aplikacja.

- Wybierz „pobierz aplikację”

- Ustaw rdzeń cortexa9_0 na „zatrzymaj się przy wejściu do programu”

- Kliknij Zastosuj i debuguj.

- Sprawdź, czy w procesie debugowania nie ma błędów

- Uważnie obserwuj robota, naciśnij przycisk Wznów, aż program zostanie uruchomiony bez trafienia w żadne punkty przerwania

- Robot powinien teraz odwrócić się i skierować w stronę głośnych dźwięków. Tak!

Krok 10: Uczynienie Ernie Autonomous

- Gdy projekt jest gotowy do pracy (możesz bez problemu uruchomić go przez debugger), możesz załadować go do pamięci flash na swojej płycie.

-

Utwórz projekt zwany „pierwszym etapem programu ładującego” (FSBL) i zawiera wszystkie instrukcje, których Twoja płyta będzie potrzebować, aby załadować pliki projektu (strumień bitów i system operacyjny) podczas uruchamiania.

- Wybierz: Plik->Nowy->Projekt aplikacji i powinno pojawić się następujące okno.

- Nazwij go, jak chcesz (np. „FSBL”)

- Upewnij się, że platforma sprzętowa jest tą, z którą pracujesz

- Naciśnij następny (nie naciskaj Zakończ)

- Wybierz szablon Zynq FSBL

- Kliknij Zakończ.

- Po zakończeniu procesu tworzenia będziesz wiedział, czy wszystko zadziałało, jeśli zobaczysz następujące dwa nowe foldery w oknie Eksploratora projektów.

-

Utwórz obraz rozruchowy Teraz musisz utworzyć obraz rozruchowy.

- Kliknij prawym przyciskiem myszy folder swojego projektu (w tym przypadku mój nazywa się „RTOSDemo”)

- Kliknij „Utwórz obraz rozruchowy” z menu rozwijanego

-

Jeśli wszystko jest poprawnie połączone, projekt będzie wiedział, jakich plików potrzebuje, a następujące okno będzie wyglądało tak, jak widać poniżej (kluczem jest to, że masz 3 partycje w sekcji Boot image, bootloader, plik bitowy i plik.elf projektów).

Jeśli tak nie jest, prawdopodobnie jest coś nie tak z połączeniem twojego projektu. Upewnij się, że foldery projektu są połączone z odpowiednimi BSP

- Kliknij przycisk „Utwórz obraz”

-

Ostatnim krokiem do wykonania w oprogramowaniu jest teraz flashowanie wcześniej utworzonego obrazu do pamięci tablicy

- Wybierz z głównego paska narzędzi SDK wybierz Xilinx Tools->Program Flash Memory

- Upewnij się, że wybrana jest właściwa platforma sprzętowa i że ścieżka pliku obrazu poprawnie wskazuje plik. BIN utworzony w poprzednim kroku.

- Wybierz „qspi single” z typu Flash

- Zaznacz „Zweryfikuj po flashu”, aby zapewnić integralność, ale nie jest to potrzebne

- Skonfiguruj swoją płytę Na koniec musisz upewnić się, że zworka trybu programowania płyty (JP5) jest prawidłowo ustawiona, aby wybrać rozruch z qspi (które zawiera to, co przed chwilą błysnęło) po uruchomieniu BootROM.

- Teraz po prostu wyłącz i włącz urządzenie i upewnij się, że dioda „Konfiguracja logiki zakończone” (LED 10) świeci na zielono.

Krok 11: Sprawienie, by Ernie był słodki

- Futro

- Dużo futra

- Duże oczy!

- … cylinder

Zalecana:

Jak zrobić bezprzewodowy telefon blaszany! (Arduino Walkie Talkie): 7 kroków (ze zdjęciami)

Jak zrobić bezprzewodowy telefon blaszany! (Arduino Walkie Talkie): Niedawno byłem w trakcie bardzo ważnej rozmowy telefonicznej, kiedy mój telefon bananowy przestał działać! Byłem tak sfrustrowany. To ostatni raz, kiedy przegapiłem połączenie z powodu tego głupiego telefonu! (Z perspektywy czasu mogłem być trochę zbyt zły w

Jak zrobić światło słoneczne do ładowania: 8 kroków

Jak zrobić światło słoneczne do ładowania:

Jak zrobić tanie i łatwe statywy głośnikowe: 8 kroków

Jak zrobić tanie i łatwe statywy pod głośniki: Nasza klasa ma nowe studio do nagrywania i montażu. Studio ma głośniki monitorowe, ale postawienie ich na biurku utrudnia słyszenie. Aby uzyskać głośniki na odpowiedniej wysokości do dokładnego słuchania, postanowiliśmy wykonać kilka podstawek pod głośniki. My

JAK ZROBIĆ ARDUINO NANO/MINI - Jak nagrać bootloader: 5 kroków

JAK ZROBIĆ ARDUINO NANO/MINI | Jak nagrać bootloader: W tej instrukcji pokażę Ci, jak zrobić Arduino MINI od podstaw.Procedura napisana w tej instrukcji może być wykorzystana do wykonania dowolnych płyt arduino zgodnie z niestandardowymi wymaganiami projektu.Obejrzyj film, aby lepiej zrozumieć

Jak zrobić kalendarz dziadków & Notatnik (nawet jeśli nie wiesz, jak to zrobić): 8 kroków (ze zdjęciami)

Jak zrobić kalendarz dziadków & Notatnik (nawet jeśli nie wiesz jak to zrobić): To bardzo ekonomiczny (i bardzo ceniony!) prezent świąteczny dla dziadków. W tym roku zrobiłem 5 kalendarzy za mniej niż 7 USD każdy.Materiały:12 wspaniałych zdjęć Twojego dziecka, dzieci, siostrzenic, siostrzeńców, psów, kotów lub innych krewnych 12 różnych elementów