Spisu treści:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:29.

- Ostatnio zmodyfikowany 2025-01-23 15:02.

Naszym celem przy tym projekcie było stworzenie czegoś, co zaoszczędzi społecznościom energię i zasoby finansowe. Lampy uliczne aktywowane ruchem zrobiłyby obie te rzeczy. W całym kraju energia jest marnowana na latarnie oświetlające puste ulice. Nasz system oświetlenia ulicznego zapewnia, że światła są włączone tylko wtedy, gdy są potrzebne, oszczędzając społecznościom niezliczone dolary. Za pomocą czujników ruchu system włącza światła tylko wtedy, gdy obecne są samochody. Również dla bezpieczeństwa pieszych wdrożyliśmy przycisk nadrzędny, który włącza wszystkie światła na ulicy. Poniższe kroki przeprowadzą Cię przez proces zaprojektowania i zbudowania naszego pomniejszonego modelu projektu przy użyciu Vivado i płyty Basys 3.

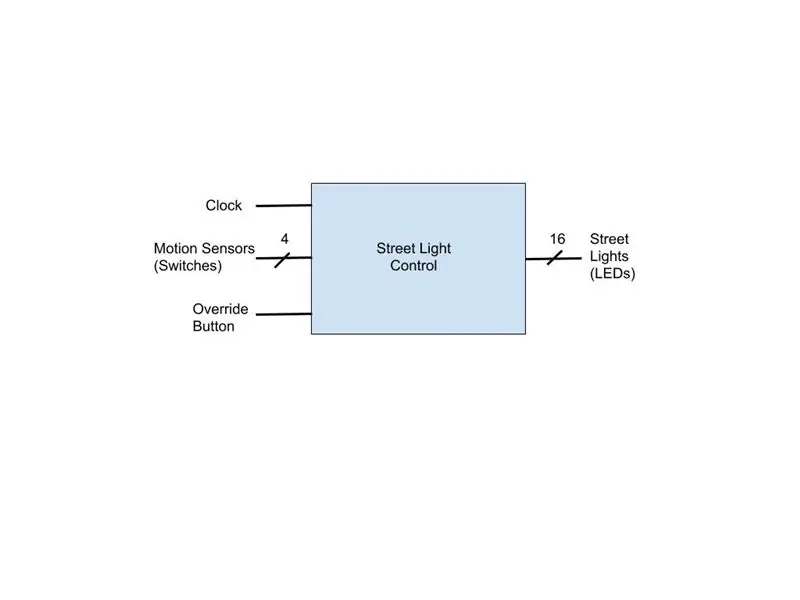

Krok 1: Czarna skrzynka systemu

Zaczęliśmy ten projekt od narysowania prostego diagramu czarnej skrzynki. Schemat czarnej skrzynki po prostu pokazuje wejścia i wyjścia, których nasz system potrzebuje do ukończenia wszystkich niezbędnych procesów. Staraliśmy się, aby nasz projekt był tak prosty i podstawowy, jak to tylko możliwe. Nasze trzy wejścia systemowe obejmowały magistralę czujników ruchu (4 w naszym pomniejszonym modelu), przycisk obejścia pieszego i wejście zegara. Z drugiej strony naszym pojedynczym wyjściem jest magistrala diod LED reprezentująca nasze latarnie uliczne. W tym modelu użyliśmy scenariusza 16 lamp ulicznych, ponieważ jest to maksymalna liczba wbudowanych wyjść LED na płycie Basys 3. Wreszcie, korzystając z tego diagramu, byliśmy w stanie stworzyć nasz projekt Vivado, pliki źródłowe i pliki ograniczeń z odpowiednimi danymi wejściowymi i wyjściowymi.

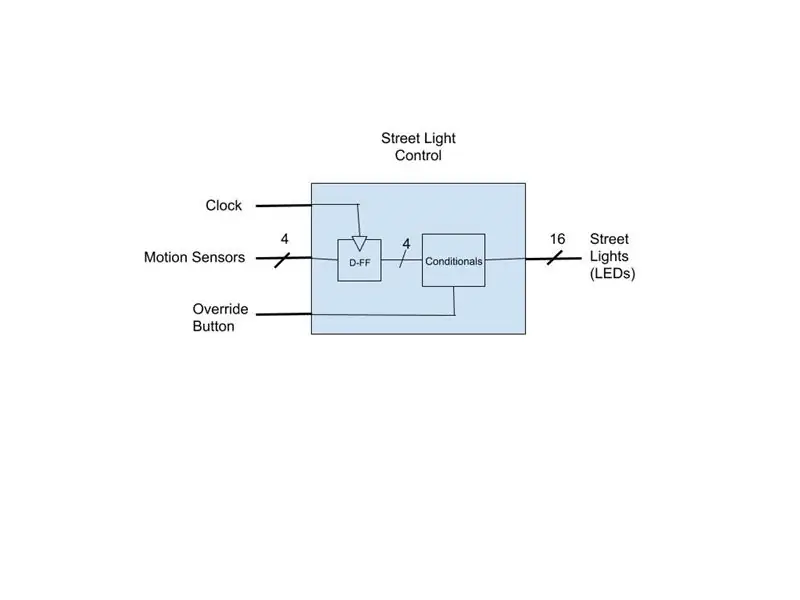

Krok 2: Komponenty

W tym kroku zanurzamy się głębiej, badając komponenty tworzące nasz diagram czarnoskrzynkowy. Naszym pierwszym komponentem jest plik źródłowy VHDL zawierający przerzutniki D. Przerzutniki D po prostu pobierają każdy sygnał z czujników na zboczu narastającym zegara i blokują te dane aż do następnego zbocza narastającego. Dzięki temu nasze wrażliwe czujniki ruchu nie powodują „migotania” wyjściowych diod LED. Ponadto, wstawiamy pojedynczy przerzutnik D na sygnał wejściowy przycisku, aby diody LED były włączone przez około 5-7 sekund po naciśnięciu przycisku. Przeprowadziliśmy to również przez dzielnik zegara.

jednostka clk_div2 to Port (clk: in std_logic; sclk: out std_logic); koniec clk_div2;

architektura my_clk_div z clk_div2 to

stała max_count: integer:= (300000000); sygnał tmp_clk: std_logic:= '0'; początek my_div: process (clk, tmp_clk) zmienna div_cnt: integer:= 0; rozpocznij if (rising_edge(clk)) then if (div_cnt = MAX_COUNT) then tmp_clk <= nie tmp_clk; div_cnt:= 0; w przeciwnym razie div_cnt:= div_cnt + 1; koniec jeśli; koniec jeśli; sclk <= tmp_clk; zakończ proces my_div; zakończ mój_clk_div;

Naszym ostatnim elementem na tym diagramie jest behawioralny plik źródłowy VHDL zawierający warunki dla wyjść oparte na konfiguracji sygnałów wejściowych.

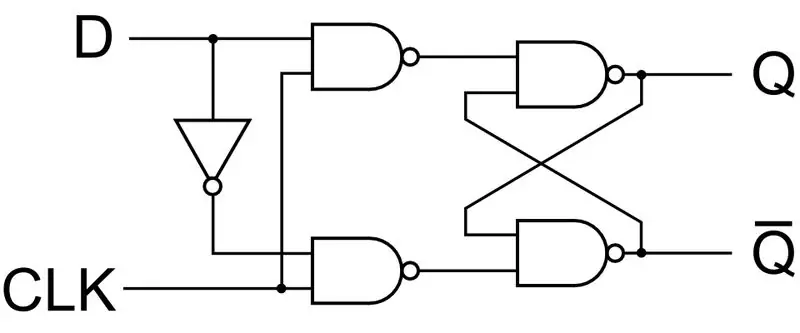

Krok 3: D Japonki

Cztery przerzutniki dołączone do sygnałów wejściowych mają zasadnicze znaczenie dla funkcjonalności naszego systemu. Jak wspomniano wcześniej, z czułymi czujnikami ruchu i przyciskiem override, klapki używają zatrzasków, aby wyprowadzać nasz sygnał wejściowy tylko na zboczu narastającym zegara. Ta sekwencyjna logika oznacza, że nasze lampy uliczne mogą pozostać włączone przez określony czas po uruchomieniu szybkim ruchem. Kodowanie D-Flip Flop jest dość proste:

beginprocess (CLK) begin if rise_edge(CLK) then Q <= D; koniec jeśli; koniec procesu;

Całość można skompilować w pojedynczą instrukcję if. Kiedy już mieliśmy ten kawałek, stworzyliśmy strukturalny plik źródłowy VHDL zawierający wszystkie cztery niezbędne klapki:

rozpocznij DFF0: mapa portów DFF (CLK => CLK, D => D(0), Q => Q(0)); DFF1: mapa portów DFF (CLK => CLK, D => D(1), Q => Q(1)); DFF2: mapa portów DFF (CLK => CLK, D => D(2), Q => Q(2)); DFF3: mapa portów DFF (CLK => CLK, D => D(3), Q => Q(3));

koniec Behawioralny;

Pomaga to utrzymać nasz główny plik strukturalny, w którym gromadzimy wszystkie komponenty systemu w znacznie bardziej uporządkowany i uporządkowany sposób.

Krok 4: Warunkowe

Aby nasz kod był zwięzły i wydajny, wszystkie warunki warunkowe napisaliśmy w jednej instrukcji case. W naszym pomniejszonym modelu mieliśmy 16 możliwych konfiguracji wyjść LED, ponieważ każdy czujnik ruchu odpowiada za grupę 4 diod LED.:

przypadek NMS jest gdy "1111" => LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED <= "1111111111111111"; sprawa końcowa;

Krok 5: Ograniczenia

Aby poprawnie określić swoje wejścia i wyjścia za pomocą Vivado, musisz zaimplementować plik ograniczenia, określający wszystkie używane porty, przyciski, diody LED i zegary.

set_property PACKAGE_PIN W5 [get_ports CLK] set_property IOSTANDARD LVCMOS33 [get_ports CLK]

set_property PACKAGE_PIN U16 [get_ports {LED[0]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED[0]}] set_property PACKAGE_PIN E19 [get_ports {LED[1]}] set_property IOSTANDARD LVCMOS33 [get_property]_AGEPIN_LED[1] U19 [get_ports {LED[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED[2]}] set_property PACKAGE_PIN V19 [get_ports {LED[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED[3]}] set_property W18 [AGE_PAGE_PAGE_P get_ports {LED[4]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED[4]}] set_property PACKAGE_PIN U15 [get_ports {LED[5]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED[5]}] set_property PACKAGE_PIN {U14 LED[6]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED[6]}] set_property PACKAGE_PIN V14 [get_ports {LED[7]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED[7]}] set_property PACKAGE_PIN V13 [get_ports 8]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED[8]}] set_property PACKAGE_PIN V3 [get_ports {LED[9]}] set_property IO STANDARD LVCMOS33 [get_ports {LED[9]}] set_property PACKAGE_PIN W3 [get_ports {LED[10]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED[10]}] set_property PACKAGE_CIN U3 [get_ports {LED[11]}] IOSTANDARD_proper LVty [get_ports {LED[11]}] set_property PACKAGE_PIN P3 [get_ports {LED[12]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED[12]}] set_property PACKAGE_PIN N3 [get_ports {LED[13]}] set_get_property LVCMOS33 IOSTAND {LED[13]}] set_property PACKAGE_PIN P1 [get_ports {LED[14]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED[14]}] set_property PACKAGE_PIN L1 [get_ports {LED[15]}] set_property IOSTANDARD {LEDget LVCMOS33 [15]}]

set_property PACKAGE_PIN U18 [get_ports BTN] set_property IOSTANDARD LVCMOS33 [get_ports BTN]

set_property PACKAGE_PIN A14 [get_ports {MS[0]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS[0]}] set_property PACKAGE_PIN A16 [get_ports {MS[1]}] set_property IOSTANDARD LVCMOS33 [get_property]_AGEPIN_PIN {MS[1]}] B15 [get_ports {MS[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS[2]}] set_property PACKAGE_PIN B16 [get_ports {MS[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS[3]}]

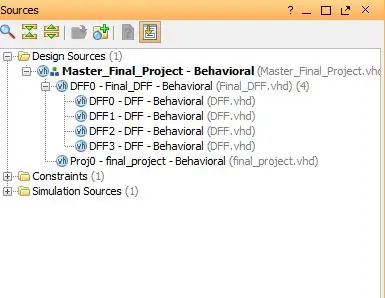

Krok 6: Główny plik źródłowy

W tym głównym pliku łączymy wszystkie wymienione wcześniej pliki źródłowe komponentów. Ten plik działa jako kod strukturalny, łączący różne komponenty.

jednostka Master_Final_Project to Port (BTN: w STD_LOGIC; CLK: w STD_LOGIC; MS: w STD_LOGIC_VECTOR (3 do 0); LED: na STD_LOGIC_VECTOR (15 do 0)); zakończenie projektu Master_Final_Project;

architektura Zachowanie Master_Final_Project to

komponent final_project to Port (--CLK: w STD_LOGIC; NMS: w STD_LOGIC_VECTOR (3 do 0); BTN: w STD_LOGIC; --sw: w STD_LOGIC_Vector (1 do 0); LED: w STD_LOGIC_VECTOR (15 do 0)); element końcowy;

komponent Final_DFF to

Port (CLK: w STD_LOGIC; D: w STD_LOGIC_Vector (3 do 0); Q: poza STD_LOGIC_Vector (3 do 0)); element końcowy;

sygnał DFF02proj30: STD_LOGIC;

sygnał DFF12proj74: STD_LOGIC; sygnał DFF22proj118: STD_LOGIC; sygnał DFF32proj1512: STD_LOGIC;

rozpocząć

DFF0: Final_DFF mapa portów (CLK => CLK, D(0) => MS(0), D(1) => MS(1), D(2) => MS(2), D(3) => MS(3), Q(0) => DFF02projekt30, Q(1) => DFF12projekt74, Q(2) => DFF22projekt118, Q(3) => DFF32projekt1512); Proj0: mapa portów final_project (NMS(0) => DFF02proj30, NMS(1) => DFF12proj74, NMS(2) => DFF22proj118, NMS(3) => DFF32proj1512, BTN => BTN, LED => LED); koniec Behawioralny;

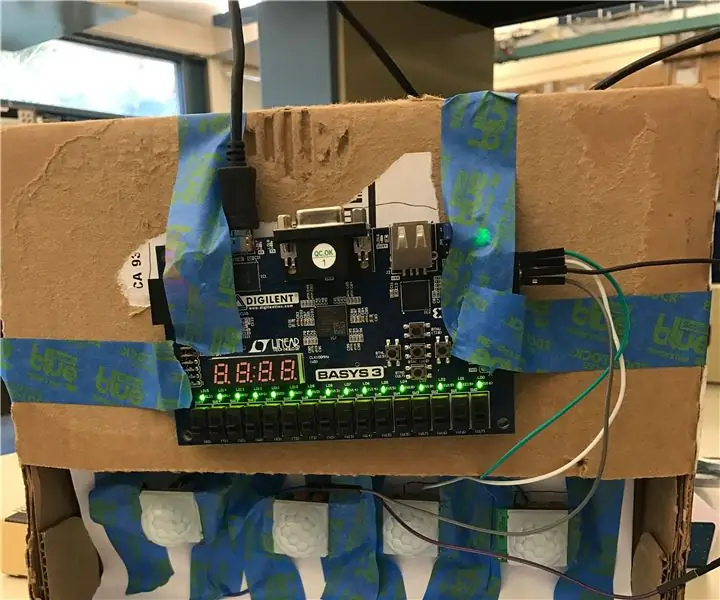

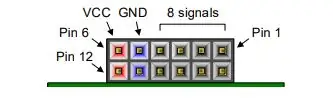

Krok 7: Montaż

Montaż sprzętu dla tego projektu jest minimalny. Jedyne wymagane elementy to:

1. Plansza Basy 3 (1)

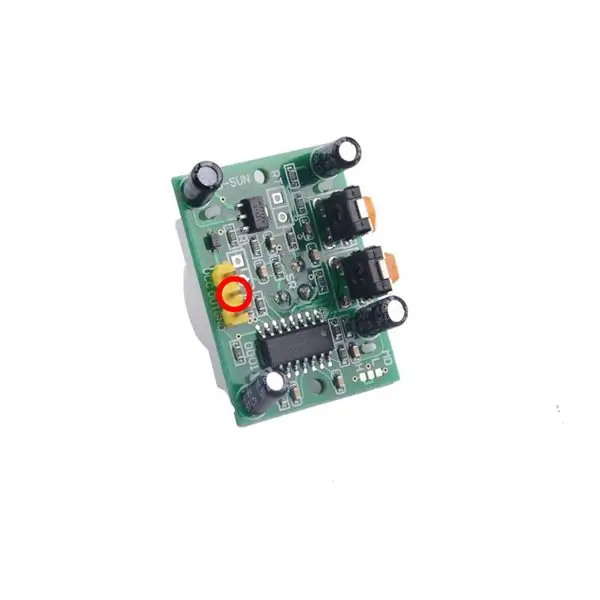

2. Tanie czujniki ruchu, które można znaleźć na amazon tutaj. (4)

3. Leady męskie-żeńskie (4)

Montaż:

1. Podłącz 4 męskie przewody do portów JB 1-4 nagłówka PMod (patrz rysunek).

2. Podłącz żeńskie końcówki do styków wyjściowych każdego czujnika ruchu.

Krok 8: Ładowanie programu

Teraz jesteśmy gotowi do załadowania głównego pliku źródłowego VHDL na płytę Basys 3. Upewnij się, że uruchomiłeś syntezę, implementację i wygenerowałeś sprawdzanie strumienia bitów pod kątem ewentualnych błędów. Jeśli wszystko przebiegnie pomyślnie, otwórz menedżera sprzętu i zaprogramuj urządzenie Basys 3. Twój projekt jest teraz gotowy!

Zalecana:

Skrzydła Cosplay aktywowane ruchem za pomocą Circuit Playground Express – część 1: 7 kroków (ze zdjęciami)

Skrzydła Cosplay aktywowane ruchem za pomocą Circuit Playground Express - część 1: Jest to pierwsza część dwuczęściowego projektu, w którym pokażę wam mój proces tworzenia pary automatycznych skrzydełek wróżek. Pierwsza część projektu to mechanika skrzydeł, a druga część to uczynienie go poręcznym i dodanie skrzydeł

Jak zrobić automatyczne oświetlenie uliczne za pomocą LM555 IC: 8 kroków

Jak zrobić automatyczne oświetlenie uliczne za pomocą układu LM555 IC: Cześć przyjacielu, dzisiaj mam zamiar wykonać obwód automatycznego oświetlenia ulicznego za pomocą układu LM555 IC. Ten obwód działa w ten sposób, gdy światło spadnie na LDR (w dzień), dioda LED nie będzie świecić a gdy światło nie będzie świecić na LDR, dioda LED zaświeci się autom

Jak zrobić automatyczne oświetlenie uliczne: 7 kroków

Jak zrobić automatyczne oświetlenie uliczne: Cześć przyjacielu, Dzisiaj zamierzam stworzyć obwód automatycznego oświetlenia ulicznego. Ten obwód będzie działał automatycznie. Rano światło zostanie automatycznie zamknięte. Ten obwód działa z LDR. Zacznijmy

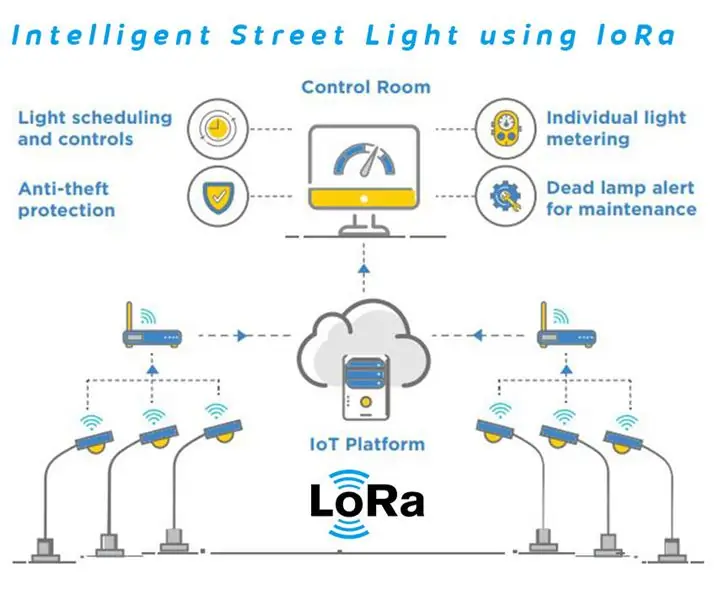

Inteligentne oświetlenie uliczne przy użyciu LoRa: 5 kroków

Inteligentne oświetlenie uliczne wykorzystujące LoRa: miejskie oświetlenie uliczne zapewnia bezpieczniejsze warunki ruchu, bezpieczniejsze środowisko dla pieszych i może stanowić znaczną poprawę wyników architektonicznych, turystycznych i komercyjnych miasta. Projekt ten ma na celu opracowanie prototypu inteligentnej ulicy

Schody aktywowane ruchem: 6 kroków (ze zdjęciami)

Schody aktywowane ruchem: Tak, wiem, co myślisz, to wydaje się trochę przesadą, ale po pierwsze, nigdy nie będziesz musiał się martwić o bicie palca u stopy, a po drugie, to sprawia, że chodzenie po schodach jest tak trudne fajnie, znalazłem się na górze bez powodu