Spisu treści:

- Krok 1: Skonfiguruj programowalną logikę Zynq dla nadajnika

- Krok 2: Skonfiguruj programowalną logikę Zynq dla odbiornika

- Krok 3: Skonfiguruj sterownik VDMA

- Krok 4: Skonfiguruj sieć Nanorouter

- Krok 5: Skonfiguruj system przetwarzania Zynq do transmisji danych przez Ethernet

- Krok 6: Skonfiguruj system przetwarzania Zynq do odbioru danych przez Ethernet

- Krok 7: Podłącz swoje płyty Zybo do źródła HDMI i zlewu HDMI

- Krok 8: Alternatywne pomysły na ulepszenia

- Krok 9: Dostępność

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:31.

- Ostatnio zmodyfikowany 2025-01-23 15:03.

Czy kiedykolwiek marzyłeś, aby móc podłączyć telewizor do komputera stacjonarnego lub laptopa jako monitor zewnętrzny, ale nie chciałeś mieć tych wszystkich nieznośnych kabli? Jeśli tak, ten samouczek jest właśnie dla Ciebie! Chociaż istnieje kilka produktów, które osiągają ten cel, projekt DIY jest znacznie bardziej satysfakcjonujący i potencjalnie tańszy.

Ta koncepcja różni się od produktów takich jak chromecast, ponieważ ma zastąpić przewód HDMI łączący się z monitorem, a nie być urządzeniem do przesyłania strumieniowego.

Nasz projekt powstał jako końcowy projekt kursu Real Time Operating Systems na California State Polytechnic University w San Luis Obispo.

Celem projektu jest wykorzystanie dwóch płyt Digilent Zybo do działania jako interfejs komunikacji bezprzewodowej między urządzeniem nadawczym HDMI (PC, Blu-ray, itp.) a urządzeniem odbiorczym HDMI (monitor biurkowy, projektor, telewizor itp.).

Jeden Digilent Zybo zostanie podłączony przez HDMI do urządzenia nadawczego, a drugi zostanie podłączony przez HDMI do urządzenia odbiorczego.

Komunikacja bezprzewodowa będzie się odbywać przy użyciu bezprzewodowej sieci lokalnej przeznaczonej dla nadajnika i odbiornika, bez konieczności kierowania przez router domowy lub inne tego typu urządzenie. Modułem bezprzewodowym użytym w tym projekcie jest nanorouter tplink wr802n, z których jeden działa jako punkt dostępowy do ustanowienia sieci, a drugi jako klient do łączenia się z siecią. Każdy nanorouter będzie podłączony kablem Ethernet do dowolnej płyty Zybo. Po podłączeniu do tych routerów urządzenia będą komunikować się przez TCP tak, jakby były połączone jednym kablem Ethernet (co oznacza, że jedyną konfiguracją potrzebną do nawiązania połączenia jest adres IP klienta).

Chociaż celem projektu było ułatwienie strumienia wideo 1080x720 przy 60 Hz, nie było to możliwe ze względu na ograniczenia przepustowości w sieci bezprzewodowej oraz brak kompresji wideo w czasie rzeczywistym w celu zmniejszenia ilości danych wymaganych do wysłania. Zamiast tego projekt ten służy jako ramy dla przyszłego rozwoju, aby osiągnąć ten cel, ponieważ ma poważnie ograniczone ograniczenia liczby klatek na sekundę, aby prawidłowo przesyłać dane HDMI zgodnie z zamierzeniami.

Wymagania projektu:

2x płytki rozwojowe Digilent Zybo (musi mieć co najmniej jeden port HDMI)

2x kable HDMI

2x kable microUSB (do podłączenia Zybo do komputera w celu rozwoju)

2x tplink wr802n nanoouters (w tym 2x microusb i zasilacze ścienne)

2x kable Ethernet

***Uwaga: Ten samouczek zakłada znajomość pakietu projektowego Vivado i doświadczenie w tworzeniu nowego projektu i projektu blokowego.***

Krok 1: Skonfiguruj programowalną logikę Zynq dla nadajnika

Nasze podejście do opracowania programowalnej logiki nadajnika polegało na wykonaniu połączenia HDMI-HDMI z komputera PC do monitora przy użyciu dwóch bloków bezpośredniego dostępu do pamięci wideo (VDMA), jednego do zapisu i jednego do odczytu.

Oba są wybierane w trybie swobodnego, 3 bufora klatek (0-1-2). Ponieważ rdzeń wideo jest zoptymalizowany do 60 klatek na sekundę, oznacza to, że VDMA zapisuje lub odczytuje nową ramkę co 16,67 ms w następującej kolejności: 0, 1, 2, 0, 1, 2, 0, 1, 2. Lokalizacje pamięci DDR dla każdej ramki są różne dla dwóch VDMA, ponieważ nie są już ze sobą zsynchronizowane. Zamiast tego do synchronizacji ruchu danych między dwoma lokalizacjami pamięci używany jest zegar sprzętowy (TTC1), skonfigurowany na 60 Hz.

Powyższy obrazek pokazuje 3 klatki, ich wymiary i ilość wymaganej pamięci (po prawej stronie klatki). Jeśli przypiszemy zapis VDMA do tych lokalizacji pamięci, możemy przypisać odczytane lokalizacje pamięci VDMA poza tym zestawem, zaczynając od 0x0B000000. Każda ramka składa się z 1280*720 pikseli, a każdy piksel składa się z 8 bitów koloru czerwonego, zielonego i niebieskiego, co daje w sumie 24 bity. Oznacza to, że ramka składa się z 1280*720*3 bajtów (2,76 MB).

Wewnątrz timera IRQ, które jest opisane w ustawieniach sterownika VDMA, obsługuje kopiowanie danych między dwoma lokalizacjami pamięci VMDA. VDMA zapewnia wskaźnik do bieżącej ramki, do której jest zapisywany lub odczytywany. Ramka jest reprezentowana przez określony szary kod, który jest konwertowany w oprogramowaniu. Definicje szarego kodu dla konfiguracji z 3 buforami ramek można znaleźć w przewodniku po produkcie AXI VDMA w dodatku C.

Pozwala nam to skopiować zapisywaną zawartość do pamięci bez czytania z ramki, do której jest aktualnie zapisywany.

***Pamiętaj, że odczyt VDMA nie jest używany podczas przesyłania danych przez sieć bezprzewodową. Jego jedynym celem jest sprawdzenie poprawności działania kopiowania pamięci z zapisu VMDA. Odczytywanie VMDA powinno być wyłączone.***

Oto kroki do utworzenia bloku projektowego nadajnika:

- Przy tworzeniu nowego projektu dobrze jest przypisać do projektu chip lub płytkę. Ten link opisuje, jak dodać nowe pliki tablicy do katalogu Vivado i powiązać właściwą tablicę z twoim projektem. Przyda się podczas dodawania bloku Processing System i przechodzenia ze sprzętu na oprogramowanie (strona SDK).

-

Dodaj następujące bloki:

- dvi2rgb

- Wejście wideo do strumienia Axi4-

- Kontroler rozrządu

- axi4-stream do wyjścia wideo

- rgb2dvi

- AXI VDMA x2

- AXI GPIO x2

- Kreator zegara

- Stały

- System przetwarzania Zynq

- Podczas dodawania systemu przetwarzania kliknij „Uruchom blokową automatyzację” na górnym zielonym pasku i upewnij się, że zaznaczona jest opcja „Zastosuj ustawienie wstępne płyty”. Wszystkie inne pozostaw domyślne.

- Obrazy każdego okna konfiguracji bloku można znaleźć na powyższych obrazach. Jeśli nie widzisz obrazu określonego okna, po prostu pozostaw go jako domyślny.

-

Rozpocznij konfigurację systemu przetwarzania Zynq:

- W konfiguracji PS-PL AXI Non Secure Włącz GP Master AXI, włącz interfejs M AXI GP0

- W PS-PL Configuration HP Slave AXI Interface włącz HP0 i HP1

- W konfiguracji MIO Upewnij się, że ENET0 jest włączony w obszarze I/O Peripherals, a następnie Application Processor Unit, włącz Timer0

- W Clock Configuration PL Fabric Clocks włącz FCLK_CLK0 i ustaw na 100 MHz.

- Kliknij OK

- Przed kliknięciem „Uruchom automatyzację połączenia” upewnij się, że połączysz bloki wideo, jak pokazano na powyższym obrazie projektu bloku TX. Będziesz chciał zmienić nazwę stałej na VDD i ustawić wartość na 1. Połącz odpowiednio bloki wideo.

- Ustaw zegar HDMI TMDS i piny danych na zewnątrz na blokach rgb2dvi i dvi2rgb

- Utwórz port wejściowy i wyjściowy dla sygnału wykrywania wtyczki hot plug (HPD) i połącz je ze sobą, są one zdefiniowane w pliku ograniczeń

-

Zegar pikselowy jest odzyskiwany z pliku TMDS_Clk_p, który jest tworzony w pliku ograniczeń. Będzie to 74,25 MHz zgodnie z rozdzielczością 720p. Ważne jest, aby zegar pikselowy (z bloku dvi2rgb) podłączyć do następujących pinów:

- vid_io_in_clk (vid do bloku strumienia Axi)

- vid_io_out_clk (strumień Axi do bloku vid out)

- clk (kontroler rozrządu)

- PixelClk (rgb2dvi)

- ***Uwaga: Obecnie, aby aktywować odzyskiwanie zegara pikseli, złącza HDMI rx i tx muszą być podłączone do aktywnego źródła/odbiornika. Jednym ze sposobów obejścia tego jest rozdzielenie bloków wideo rx i tx na różne domeny zegara (innymi słowy, wygenerowanie nowego zegara 74,25 MHz do zasilania bloku tx).***

- Następnie skonfiguruj kreatora zegara tak, aby mieć wejście 100 MHz (globalne źródło bufora) i 3 zegary wyjściowe @ 50 MHz (zegar AXI-Lite), 150 MHz (zegar AXI4-Stream), 200 MHz (pin dvi2rgb RefClk).

- Podłącz pin systemu przetwarzania FCLK_CLK0 do wejścia kreatora zegara

- W tym momencie kliknij „Uruchom automatyzację połączeń” na zielonym pasku u góry okna projektu. Dobrym pomysłem jest robienie tego dla jednego bloku na raz i postępowanie zgodnie z powyższym obrazem projektu bloku TX.

- Narzędzie spróbuje dodać AXI Interconnect, który działa jako połączenie master/slave dla bloków korzystających z magistrali AXI-Lite (VDMA i GPIO).

- Doda również AXI SmartConnect, który działa jako połączenie master/slave dla interfejsów procesorów AXI4-Stream i High Performance używanych przez VDMA (Stream to Memory Map i odwrotnie).

- Narzędzie doda również reset systemu procesora. Upewnij się, że jest on podłączony tylko do bloków związanych z VDMA, GPIO i procesorem. Nie podłączaj go do żadnych bloków wideo (tj. dvi2rgb, kontroler czasu, vid to stream itp.)

- Po zakończeniu automatyzacji połączeń sprawdź, czy połączenia są zgodne z obrazem projektu bloku TX. Zauważysz dodatkowy blok System ILA, o którym nie wspomniano. Służy tylko do debugowania i na razie nie jest potrzebne. Wykorzystuje reset procesora 150M, więc to również nie jest potrzebne. Wszędzie widać małe zielone "błędy" na autobusach, to z powodu ILA i można je zignorować.

- Ostatnim krokiem jest kliknięcie prawym przyciskiem myszy projektu bloku w drzewie źródeł projektu i wybranie opcji „Create HDL Wrapper”. Jeśli planujesz dodać logikę do opakowania, zostanie ona nadpisana za każdym razem, gdy zostanie wybrana.

- Zobacz sekcję Konfiguracja sterownika VDMA, aby uzyskać szczegółowe informacje na temat strony SDK.

Zegary i resety

Odkryłem, że najważniejszymi aspektami każdego projektu logiki programowalnej jest staranne rozważenie domen zegara i sygnałów resetujących. Jeśli są one odpowiednio skonfigurowane, masz dobrą szansę na to, aby Twój projekt działał.

Zegar pikseli i synchronizacja zablokowane

W celu sprawdzenia, czy określone sygnały są aktywne, dobrym pomysłem jest powiązanie tych sygnałów z diodami LED (zegary, resety, blokady itp.). Dwa sygnały, które okazały się pomocne w śledzeniu na płytce nadajnika, to zegar pikselowy i sygnał „zablokowany” w bloku wyjścia wideo AXI4-Stream, który informuje, że taktowanie wideo zostało zsynchronizowane z kontrolerem taktowania i źródłem wideo dane. Dodałem trochę logiki do opakowania bloku projektu, które śledzi zegar pikseli przy użyciu sygnału PixelClkLocked w bloku dvi2rgb jako resetu. Załączam plik jako hdmi_wrapper.v tutaj. W tym miejscu znajduje się również plik z ograniczeniami.

Krok 2: Skonfiguruj programowalną logikę Zynq dla odbiornika

Blok programowalnej logiki dla odbiornika jest prostszy. Kluczową różnicą, inną niż brakujące bloki wejściowe hdmi, jest brak odzyskanego zegara pikselowego. Z tego powodu musimy wygenerować własny z kreatora zegara. Projekt ten powinien być wykonany w odrębnym projekcie od nadajnika. Dla naszych celów projekt odbiornika był zgodny z płytą Zybo 7Z-20, podczas gdy nadajnik był zgodny z płytą Z7-10. Układy FPGA na płytach są różne, więc… bądź ostrożny.

Oto kroki do utworzenia bloku projektowego odbiornika:

-

Dodaj następujące bloki ip do swojego projektu:

- Kontroler rozrządu

- AXI4-Stream do wyjścia wideo

- RGB na DVI

- AXI VDMA

- AXI GPIO

- System przetwarzania

- Kreator zegara

- Stała (VDD ustawione na 1)

- Postępuj zgodnie z tym samym wzorcem, aby skonfigurować te bloki jako nadajnik. Zdjęcia przedstawiające zauważalne różnice w konfiguracji znajdują się tutaj. Pozostałe pozostają takie same jak nadajnik.

- Skonfiguruj VDMA dla tego projektu jako kanał tylko do odczytu. Wyłącz kanał zapisu.

-

Kreator zegara należy skonfigurować dla następujących wyjść:

- clk_out1: 75 MHz (zegar pikseli)

- clk_out2: 150 MHz (taktowanie strumienia)

- clk_out3: 50 MHz (zegar Axi-lite)

- Połącz bloki wideo, jak pokazano na rysunku projektu bloku RX.

- Następnie uruchom automatyzację połączeń, która doda bloki AXI Interconnect, AXI SmartConnect oraz System Reset i spróbuje wykonać odpowiednie połączenia. Przejdź tutaj powoli, aby upewnić się, że nie wykonuje niechcianych połączeń.

- Ustaw zegar HDMI TMDS i piny danych na zewnątrz na bloku rgb2dvi

- Nie ma potrzeby podłączania sygnału podczas pracy w tym projekcie.

Krok 3: Skonfiguruj sterownik VDMA

Konfiguracja dla różnych bloków, które są konfigurowane za pomocą interfejsu AXI-Lite, najlepiej wykonać, korzystając z projektów demonstracyjnych dołączonych do BSP jako odniesienia. Po wyeksportowaniu sprzętu projektowego i uruchomieniu SDK z Vivado, będziesz chciał dodać nowy pakiet obsługi płyty i dołączyć bibliotekę lwip202 w oknie ustawień BSP. Otwórz plik system.mss z BSP, a zobaczysz sterowniki peryferyjne obecne w twoim projekcie bloku. Opcja „Importuj przykłady” umożliwia importowanie projektów demonstracyjnych, które wykorzystują te urządzenia peryferyjne, a tym samym pokazuje, jak skonfigurować je w oprogramowaniu przy użyciu dostępnych sterowników Xilinx (patrz załączony obrazek).

Była to metoda używana do konfiguracji VDMA, Timer & Interrupt oraz GPIO. W tym miejscu zawarto kod źródłowy zarówno dla nadawania, jak i odbioru. Różnice dotyczą prawie wyłącznie main.c.

***UWAGA: Ponieważ system nie jest w pełni funkcjonalny w momencie pisania tego samouczka, kod źródłowy w tej sekcji nie zawiera kodu sieci bezprzewodowej. W wyniku połączenia projektów transmisji/odbioru rdzenia wideo z projektami transmisji/odbioru sieci należy rozwiązać kilka błędów. Dlatego ten samouczek traktuje je na razie osobno.***

Funkcja obsługi przerwań TX (IRQHandler)

Ta funkcja odczytuje szare kody dostarczane przez VDMA do odczytu i zapisu za pośrednictwem bloków GPIO. Szare kody są konwertowane na dziesiętne i używane do wyboru podstawowej lokalizacji pamięci ramki dla bieżącej ramki. Kopiowana ramka jest poprzednią ramką do tej, do której VDMA zapisuje (np. jeśli VDMA zapisuje do ramki 2, kopiujemy ramkę 1; jeśli zapisuje do ramki 0, zawijamy i czytamy z ramki 2).

Funkcja przechwytuje tylko co szóstą klatkę, aby zmniejszyć częstotliwość klatek do 10 Hz zamiast 60 Hz. Górna granica sieci to 300 Mb/s. Przy 10 klatkach na sekundę wymagana jest przepustowość 221,2 Mb/s.

Komentowanie/odkomentowanie dwóch linii w tej funkcji pozwoli użytkownikowi przejść do trybu HDMI passthru w celach debugowania/testu (komentowany kod wskazuje odpowiednie linie). Obecnie kopiuje ramkę do lokalizacji w pamięci używanej przez kod ethernetowy.

Funkcja obsługi przerwań RX (IRQHandler)

Ta funkcja jest bardzo podobna do funkcji TX, ale kopiuje z 2 bufora FIFO używanego przez sieć Ethernet do zapisywania przychodzących danych. Kod ethernetowy wskazuje, która ramka jest zapisywana w FIFO, dane są kopiowane z przeciwległej ramki. Dane są kopiowane do ramki bezpośrednio za tą, która jest odczytywana przez VDMA, aby uniknąć rozerwania.

Krok 4: Skonfiguruj sieć Nanorouter

Aby stworzyć sieć za pomocą nanorouterów TPlink, włącz je indywidualnie i połącz się z domyślnym SSID Wi-Fi dla urządzeń. Więcej informacji na temat ustawień konfiguracyjnych dla tego konkretnego urządzenia można znaleźć w instrukcji obsługi urządzenia.

Skonfiguruj jedno z urządzeń jako punkt dostępowy, które będzie działać jako podstawowe połączenie z siecią. Upewnij się, że nazwałeś sieć i zanotuj nazwę oraz wyłącz DHCP (nie chcemy, aby router dynamicznie konfigurował adresy IP, chcemy, aby płyty Zybo nadawczo-odbiorcze ustawiały swoje adresy IP, aby były spójne). Po skonfigurowaniu upewnij się, że urządzenie uruchomi się ponownie i ustanowi tę sieć.

Skonfiguruj drugie urządzenie jako klienta i upewnij się, że łączy się z siecią SSID skonfigurowaną w pierwszym nanorouterze. Jeszcze raz upewnij się, że DHCP jest wyłączony dla klienta.

Po zakończeniu i ponownym uruchomieniu klient powinien połączyć się z nanorouterem punktu dostępowego (jeśli tak się nie stanie, prawdopodobnie występuje problem z konfiguracją jednego z urządzeń). Zauważysz, że dioda LED na kliencie będzie świecić stałym światłem po połączeniu się z punktem dostępowym.

W tym momencie dioda LED nanoroutera punktu dostępowego prawdopodobnie nadal będzie migać, jest to w porządku! Migające światło oznacza, że nie jest on podłączony do innego urządzenia z portu Ethernet, a po podłączeniu do skonfigurowanego Zybo dioda LED będzie świecić światłem ciągłym, wskazując na udane połączenie sieciowe.

Teraz, gdy mamy skonfigurowane nasze nanorutery, mamy sieć bezprzewodową, która pozwoli nam się komunikować. Ważną uwagą jest to, że nasza metoda konfiguracji dla nanorouterów (jako punkt dostępowy i klient) pozwala nam komunikować się z transmitującej płyty Zybo do odbierającej płyty Zybo tak, jakby obie były połączone jednym przewodem Ethernet. To sprawia, że konfiguracja naszej sieci jest mniej trudna, ponieważ alternatywa prawdopodobnie obejmowałaby konfigurację płyt Zybo w celu bezpośredniego połączenia z serwerem wraz z zamierzonym połączeniem.

Po skonfigurowaniu obu urządzeń nanorutery są skonfigurowane i gotowe do wdrożenia w sieci WIDI. Nie ma konkretnego parowania między nanoruterami a płytami Zybo, ponieważ punkt dostępowy lub klient będą działać zarówno dla urządzenia nadawczego, jak i odbiorczego.

Krok 5: Skonfiguruj system przetwarzania Zynq do transmisji danych przez Ethernet

Aby przesłać dane HDMI z jednej płyty Zybo na drugą, musimy włączyć protokół Ethernet w naszym sterowniku VDMA. Naszym celem jest przesyłanie strumieniowe pojedynczych klatek wideo przez urządzenie peryferyjne Ethernet w systemie przetwarzania z ustaloną szybkością zgodną z przepustowością naszej sieci. W naszym projekcie wykorzystaliśmy TCP dostarczony przez bare-metal LwIP API. Ponieważ obaj członkowie projektu nie mają doświadczenia w narzędziach sieciowych, wybór ten został dokonany bez pełnego rozpoznania implikacji i ograniczeń związanych z TCP. Głównym problemem tej implementacji była ograniczona przepustowość i fakt, że tak naprawdę nie jest ona zaprojektowana do przesyłania dużych ilości danych. Alternatywne rozwiązania zastępujące TCP i ulepszające w tym projekcie zostaną omówione później.

Krótki opis protokołu TCP z LwIP: Dane są przesyłane przez sieć w pakietach o rozmiarze tcp_mss (maksymalny rozmiar segmentu protokołu TCP), który zwykle wynosi 1460 bajtów. Wywołanie tcp_write zajmie trochę danych, do których odwołuje się wskaźnik, i skonfiguruje pbufs (bufory pakietów) do przechowywania danych i zapewnienia struktury dla operacji TCP. Maksymalna ilość danych, które można umieścić w kolejce jednocześnie, jest ustawiona jako tcp_snd_buf (przestrzeń bufora nadawcy TCP). Ponieważ ten parametr jest liczbą 16 bitową, jesteśmy ograniczeni do rozmiaru bufora wysyłania wynoszącego 59695 bajtów (jest wymagane wypełnienie bufora wysyłania). Po umieszczeniu danych w kolejce wywoływane jest tcp_output, aby rozpocząć transmisję danych. Przed wysłaniem kolejnego segmentu danych konieczne jest, aby wszystkie poprzednie pakiety zostały pomyślnie przesłane. Ten proces jest wykonywany za pomocą funkcji recv_callback, ponieważ jest to funkcja wywoływana, gdy odbiorca widzi potwierdzenie.

Wykorzystanie przykładowych projektów w Vivado SDK jest bardzo pomocne w nauce działania protokołu LwIP TCP i jest dobrym punktem wyjścia do rozpoczęcia nowego projektu.

Procedura dla urządzenia nadawczego WiDi jest następująca:

- Zainicjuj sieć TCP za pomocą wywołań funkcji sterownika bare-metal LWIP.

- Określ wszelkie funkcje wywołania zwrotnego niezbędne do operacji sieciowych.

- Połącz się z odbiornikiem WiDi, łącząc się z jego adresem IP i portem (nasza konfiguracja: IP odbiornika to 192.168.0.9, podłącz do portu 7).

- Gdy licznik czasu sterownika VDMA wygaśnie, wprowadź TX ISR.

- Określ bieżący bufor ramki, do którego chcesz uzyskać dostęp, na podstawie szarego kodu VDMA

- Ustaw w kolejce pierwszy segment danych w buforze wysyłania TCP

- Wyprowadzanie danych i aktualizowanie zmiennych lokalnych, aby śledzić, ile danych zostało wysłanych w bieżącej ramce.

- Po dotarciu do odebranego wywołania zwrotnego (wywołanie funkcji wykonane po otrzymaniu przez nadajnik potwierdzenia pobrania danych) kolejkuje się kolejny segment danych.

- Powtarzaj kroki 7 i 8, aż cała ramka zostanie wysłana.

- Powróć do stanu bezczynności, aby czekać na następne przerwanie zegara wskazujące, że nowa ramka jest gotowa (powrót do kroku 4).

Upewnij się, że skonfigurowałeś ustawienia pakietu obsługi płyty LwIP, jak pokazano na powyższym obrazku. Wszystkie wartości są domyślne z wyjątkiem tcp_snd_buf, tcp_pueue_ooseq, mem_size, memp_n_tcp_seg. Należy również zauważyć, że szczegółowe debugowanie można uzyskać, zmieniając parametry BSP dla grupy debug_options.

Krok 6: Skonfiguruj system przetwarzania Zynq do odbioru danych przez Ethernet

Płytka rozwojowa Zybo, która będzie działać jako odbiornik bezprzewodowy, będzie działać podobnie do urządzenia nadawczego. Ustawienia pakietu wsparcia płyty dla LwIP będą takie same jak w poprzednim kroku.

Urządzenie przyjmie pakiety zawierające segmenty ramek wideo z nanoroutera i skopiuje dane ramki wideo do potrójnej przestrzeni bufora ramek dla odbierającego VDMA. Aby uniknąć nadpisywania jakichkolwiek danych, podczas zbierania danych z nanoroutera używany jest podwójny bufor danych (nazywamy go buforem sieciowym), dzięki czemu ruch sieciowy może być nadal przesyłany strumieniowo, podczas gdy poprzednia pełna klatka wideo jest kopiowana do Bufor VDMA.

Procedura dla urządzenia odbiorczego WiDi wymaga dwóch zadań, z których jedno to odbieranie danych Ethernet, a drugie to kopiowanie ramek wideo z bufora sieciowego do potrójnego bufora ramek VDMA.

Zadanie odbioru Ethernet:

- Zainicjuj sieć TCP za pomocą wywołań funkcji sterownika bare-metal LWIP (ustaw z adresem IP, z którym połączy się nadajnik, w naszym 192.168.0.9)

- Określ wszelkie funkcje wywołania zwrotnego niezbędne do operacji sieciowych.

- Po odebraniu pakietu Ethernet skopiuj dane pakietu do bieżącego bufora sieciowego, zwiększ ilość zgromadzonych danych.

- Jeśli pakiet wypełnia bufor ramki sieci, przejdź do kroków 5 i 6. W przeciwnym razie wróć do kroku 3 z tego zadania.

- sygnał, że zadanie potrójnego bufora ramki VDMA powinno skopiować z nowo ukończonego bufora sieciowego.

- Przełącz się na inny bufor sieciowy i kontynuuj zbieranie danych przez Ethernet.

- Bezczynny do momentu odebrania nowego pakietu Ethernet (krok 3).

Skopiuj bufor sieciowy do potrójnego bufora ramki VDMA:

- Gdy licznik czasu sterownika VDMA wygaśnie, wprowadź RX ISR.

- Określ bieżący bufor ramki, do którego chcesz uzyskać dostęp, na podstawie szarego kodu VDMA.

- Określ, który bufor sieciowy zostanie skopiowany do bufora VDMA, i skopiuj te dane

Krok 7: Podłącz swoje płyty Zybo do źródła HDMI i zlewu HDMI

Teraz podłącz kable hdmi do odbiornika i nadajnika, zaprogramuj układy FPGA i uruchom system przetwarzania. Szybkość klatek będzie prawdopodobnie bardzo niska ze względu na ogromne obciążenie operacji LwIP i ograniczoną przepustowość. Jeśli są jakieś problemy, połącz się przez UART i spróbuj zidentyfikować ostrzeżenia lub błędy.

Krok 8: Alternatywne pomysły na ulepszenia

Dużym problemem dla tego projektu była ilość danych potrzebnych do przesłania przez Wi-Fi. Spodziewaliśmy się tego, jednak nie doceniliśmy wpływu, jaki miałoby to mieć i spowodowało więcej serii obrazów na ekranie, a nie wideo. Istnieje kilka sposobów na ulepszenie tego projektu:

- Kompresja wideo w czasie rzeczywistym. Kompresja przychodzącego strumienia wideo klatka po klatce znacznie zmniejszyłaby ilość danych potrzebnych do przesłania przez sieć. Najlepiej byłoby, gdyby zostało to zrobione sprzętowo (co nie jest łatwym zadaniem) lub można to zrobić w oprogramowaniu, używając drugiego rdzenia ARM do uruchomienia algorytmów kompresji (byłoby to wymagać dalszej analizy, aby upewnić się, że czas działa). Istnieje kilka komponentów do kompresji wideo w czasie rzeczywistym typu open source, które znaleźliśmy w Internecie, ale większość to IP.

- Implementacja strumienia Ethernet w sprzęcie, a nie w oprogramowaniu. Było mnóstwo narzutu z powodu braku miejsca dostępnego do kolejkowania danych wychodzących w nadajniku, ze względu na ograniczenie rozmiaru segmentu. Znacznie bardziej wydajnym procesem jest użycie AXI Ethernet IP z buforem FIFO lub DMA do wprowadzania do niego danych. Zmniejszyłoby to dodatkowy bagaż z LwIP TCP i umożliwiłoby większy przepływ danych.

Krok 9: Dostępność

Produktem końcowym tego projektu WiDi powinna być w pełni zintegrowana, kompaktowa para urządzeń, które użytkownik może podłączyć do dowolnego źródła HDMI, a następnie bezprzewodowo przesłać obraz wideo do wyświetlacza z funkcją HDMI. Urządzenia miałyby być wyposażone w Zynq-7000 SoC znajdujący się na płycie referencyjnej Zybo i zawierać sprzęt sieciowy znajdujący się w nanorouterach TP-Link. Idealnie, użytkownik byłby w stanie sterować modułem nadawczym z odrębnej lokalizacji w docelowym systemie operacyjnym, przy niewielkiej potrzebie posiadania znacznych zdolności technicznych.

Bezpieczeństwo i łączność

Urządzenia powinny również obejmować Transport Layer Security (TLS) i mieć ograniczoną zdolność automatycznego łączenia, zarówno ze względu na ochronę prywatności. Intencją projektantów jest, aby połączenie z wyświetlaczem za pośrednictwem interfejsu bezprzewodowego było celowym działaniem w imieniu użytkownika, aby uniknąć błędnego nadawania poufnych materiałów.

Aktualny status

Do tego momentu stan projektu jest nadal w toku. Aby bieżący użytkownik punktu końcowego mógł skorzystać z tego samouczka, musi on dobrze rozumieć techniczne projektowanie systemów wbudowanych i powinien mieć pewną wiedzę na temat współpracy programowalnego sprzętu i oprogramowania wbudowanego.

Dane przesyłane przez sieć nie są w tym momencie szyfrowane i zakłada się, że są to czysta transmisja pakietów TCP/IP.

Projekt rdzenia wideo został pomyślnie przetestowany zarówno pod kątem transmisji, jak i odbioru. Z drugiej strony nawiązano połączenie bezprzewodowe między dwiema płytami zybo i pomyślnie przesłano dane ramki testowej. Nadal jednak konieczne jest łączenie kodu sieciowego z każdym projektem rdzenia wideo i testowanie transmisji rzeczywistych klatek wideo.

Zalecana:

Gra 3d Maze przy użyciu Arduino: 8 kroków (ze zdjęciami)

Gra w labirynt 3D przy użyciu Arduino: Cześć przyjaciele, więc dzisiaj zamierzamy stworzyć grę w labirynt przy użyciu ARDUINO UNO. Ponieważ Arduino Uno jest najczęściej używaną planszą, bardzo fajnie jest tworzyć z nią gry. W tej instrukcji stwórzmy grę w labirynt, którą steruje się za pomocą joysticków.Nie zapomnij

Neopixel Ws2812 Rainbow LED Glow z M5stick-C - Uruchamianie Rainbow na Neopixel Ws2812 przy użyciu M5stack M5stick C przy użyciu Arduino IDE: 5 kroków

Neopixel Ws2812 Rainbow LED Glow z M5stick-C | Uruchamianie Rainbow na Neopixel Ws2812 Używając M5stack M5stick C Używając Arduino IDE: Cześć chłopaki, w tej instrukcji dowiemy się, jak używać neopikselowych ws2812 LED lub taśmy LED lub matrycy LED lub pierścienia LED z płytką rozwojową m5stack m5stick-C z Arduino IDE i zrobimy wzór tęczy z nim

Przetwarzanie wideo przy użyciu VHDL i Zybo: 10 kroków

Przetwarzanie wideo przy użyciu VHDL i Zybo: FPGA są szybsze niż procesory w przetwarzaniu, ponieważ mogą wykonywać wiele obliczeń równolegle Uwaga: Ten projekt jest wciąż w budowie i będzie ulepszany (jak tylko będę miał czas). W międzyczasie podróżuję po świecie

Quadkopter przy użyciu płyty Zybo Zynq-7000: 5 kroków

Quadcopter Korzystanie z płyty Zybo Zynq-7000: Zanim zaczniemy, oto kilka rzeczy, które chcesz dla projektu: Lista części 1x płyta Digilent Zybo Zynq-7000 1x rama quadkoptera z możliwością zamontowania Zybo (załączony plik Adobe Illustrator do cięcia laserowego) 4x Turnigy D3530/ 14 silników bezszczotkowych 1100KV 4x

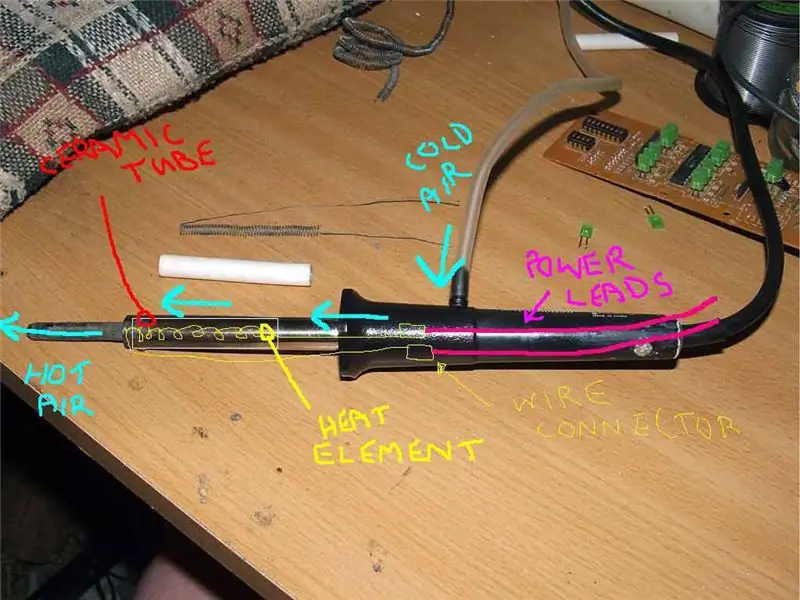

DIY lutownica na gorące powietrze przy użyciu 12-18 woltów prądu stałego przy 2-3 amperach: 18 kroków (ze zdjęciami)

DIY lutownica na gorące powietrze przy użyciu 12-18 woltów prądu stałego przy 2-3 amperach: to moja pierwsza publikacja eva artykułu o majsterkowaniu w Internecie. Więc przepraszam za literówki, protokoły itp. Poniższe instrukcje pokazują, jak zrobić PRACOWĄ lutownicę na gorące powietrze odpowiednią do WSZYSTKICH zastosowań wymagających lutowania. To lutowanie gorącym powietrzem