Spisu treści:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:29.

- Ostatnio zmodyfikowany 2025-01-23 15:02.

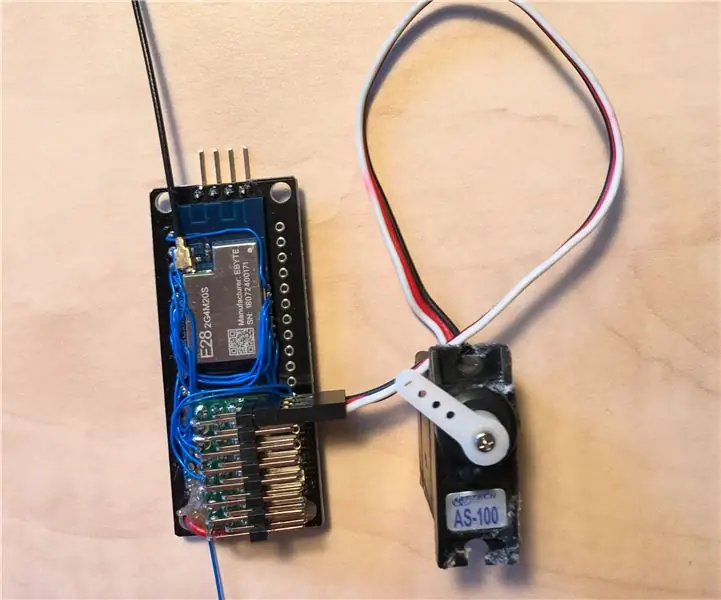

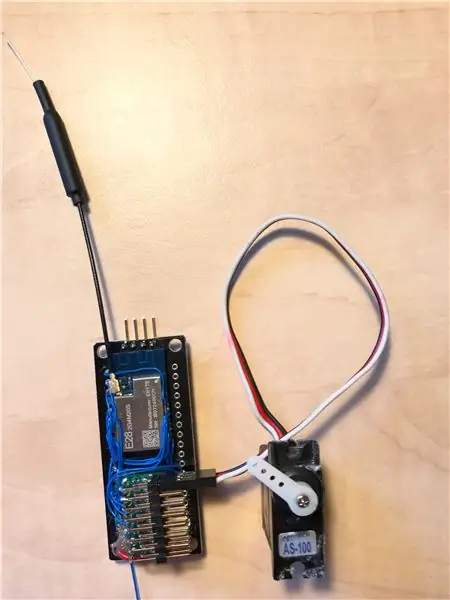

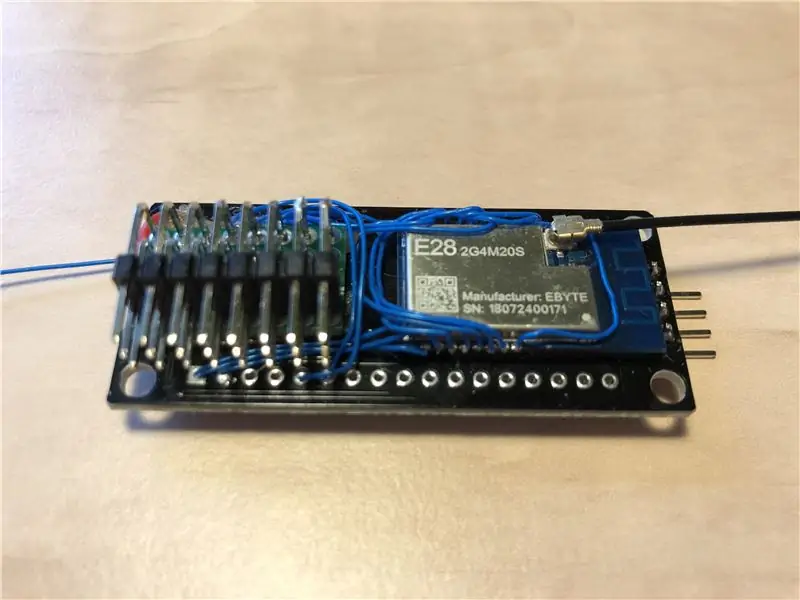

Obecnie buduję nadajnik/odbiornik RC w oparciu o chip SX1280 RF. Jednym z celów projektu jest to, że chcę mieć 12-bitową rozdzielczość serwo, od drążków aż do serwomechanizmów. Częściowo dlatego, że nowoczesne serwa cyfrowe mają rozdzielczość 12 bitów, a po drugie wysokiej klasy nadajnik i tak używa 12 bitów. Badałem, w jaki sposób mogę generować sygnały PWM o wysokiej rozdzielczości na urządzeniach STM32. W tej chwili do prototypu używam czarnej pigułki (STM32F103C8T8).

Krok 1: Lista części

Sprzęt komputerowy

- Dowolna płytka rozwojowa STM32F103 (niebieska pigułka, czarna pigułka itp.)

- Power bank USB jako zasilacz

- Programator STM32 (Segger j-links, ST-LINK/V2 lub po prostu klon st-link)

Oprogramowanie

- STM32CubeMX

- Atoliczne TrueSTUDIO dla STM32

- Źródło projektu z github

Krok 2: Oczywiste rozwiązanie

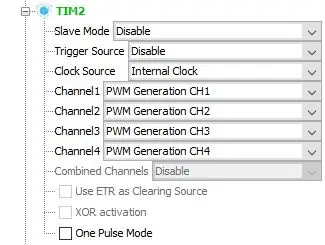

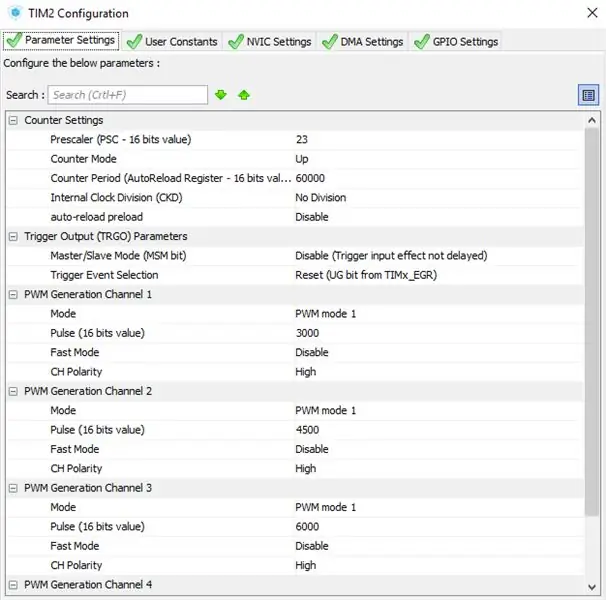

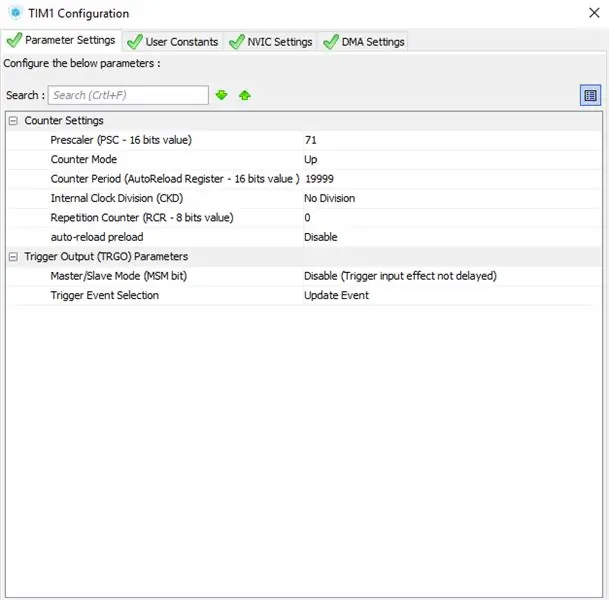

Prawdopodobnie najłatwiejszym rozwiązaniem jest użycie jednego z timerów, który może generować sygnały PWM, jak TIM1-3 na STM32F103. W przypadku nowoczesnego serwa cyfrowego częstotliwość odświeżania może spaść do około 5 ms, ale w przypadku starego serwa analogowego powinna wynosić 20 ms lub 50 Hz. Tak więc, jako najgorszy scenariusz, wygenerujmy to. Z zegarem 72 MHz i 16-bitową rozdzielczością licznika timera musimy ustawić preskaler timera na minimum 23, aby pokryć częstotliwość 20 ms. Wybrałem 24, ponieważ potem przez 20 ms muszę ustawić licznik dokładnie na 60000. Na zrzutach ekranu widać konfigurację CubeMX i wygenerowane sygnały PWM 1 i 1,5 ms. Niestety na 1ms licznik timera powinien być ustawiony na 3000, co dałoby nam tylko 11 bitową rozdzielczość. Nieźle, ale cel był 12 bitowy, więc spróbujmy czegoś innego.

Oczywiście, gdybym wybrał mikrokontroler z 32-bitowym licznikiem timera, taki jak STM32L476, ta rozdzielczość może być znacznie wyższa i problem zostałby rozwiązany.

Ale tutaj chciałbym zaproponować alternatywne rozwiązanie, które jeszcze bardziej zwiększy rozdzielczość nawet na STM32F103.

Krok 3: Liczniki kaskadowe dla wyższej rozdzielczości

Główny problem z poprzednim rozwiązaniem polega na tym, że liczba klatek na sekundę (20 ms) jest stosunkowo wysoka w porównaniu z faktycznie generowanym sygnałem PWM (od 1 do 2 ms), więc marnujemy niektóre wartościowe bity na pozostałe 18 ms, gdy czekamy na następna ramka. Można to rozwiązać przez kaskadowanie zegarów przy użyciu funkcji połączenia zegarów do synchronizacji.

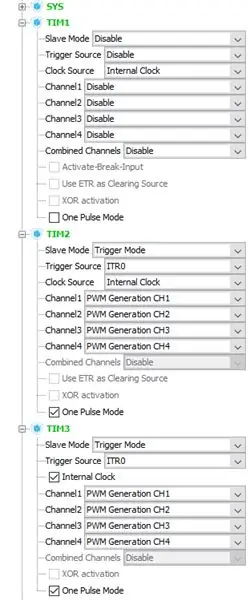

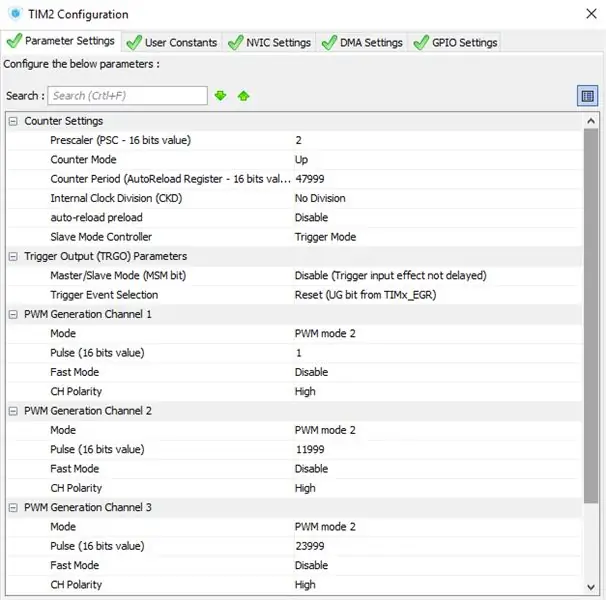

Pomysł jest taki, że użyję TIM1 jako mastera do generowania szybkości klatek (20 ms), a TIM2, TIM3 do radzenia sobie z sygnałami PWM jako slave. Gdy urządzenie nadrzędne wyzwala urządzenia podrzędne, generują one sygnał PWM tylko w trybie jednego impulsu. Dlatego w tych zegarach wystarczy mi pokrycie 2 ms. Na szczęście możesz kaskadować te zegary w sprzęcie, więc ta synchronizacja nie wymaga ingerencji procesora i jest również bardzo precyzyjna, jitter jest w regionie ps. Możesz zobaczyć konfigurację CubeMX na zrzutach ekranu.

Jak widać wybrałem 3 jako preskalarne więc dla 2 ms muszę ustawić 48000 w liczniku timera. Daje nam to 24000 na 1 ms, co w rzeczywistości jest więcej niż potrzebujemy do rozdzielczości 14-bitowej. Taaaaa…

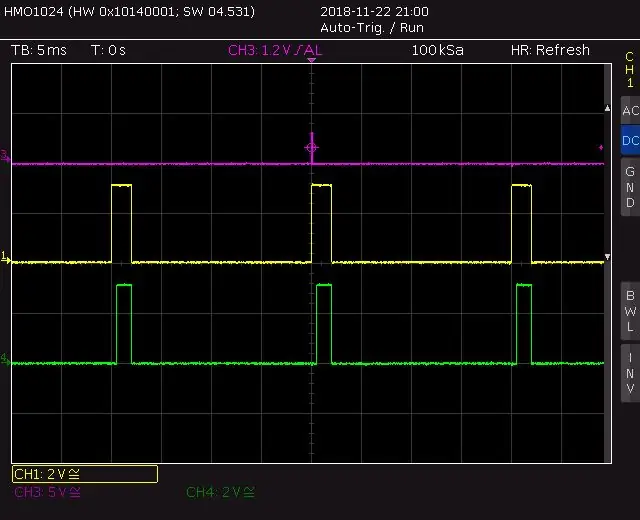

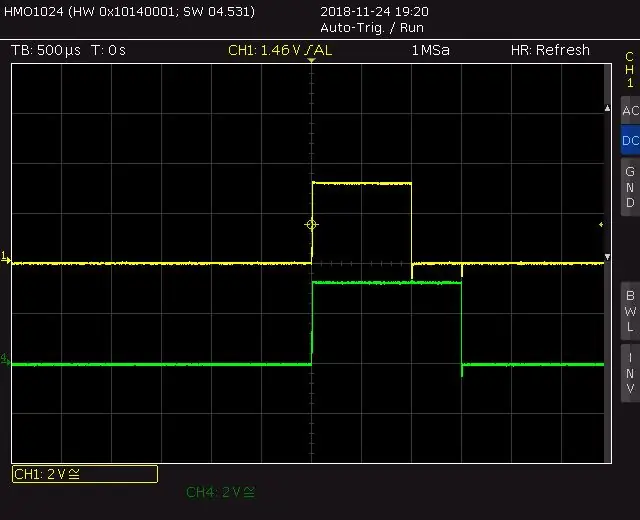

Proszę spojrzeć na zrzuty ekranu oscyloskopu we wstępie, aby uzyskać ostateczny wynik. Kanał 3 (fioletowy) to przerwanie głównego timera, które spowoduje wyzwolenie maści w celu wygenerowania jednego impulsu. Kanały 1 i 4 (żółta i zielona wiązka) to rzeczywiste sygnały PWM generowane przez różne zegary. Zauważ, że są zsynchronizowane, ale są zsynchronizowane na krawędziach spływu, to jest z powodu trybu PWM 2. To nie jest problem, ponieważ szybkość PWM dla konkretnego serwa jest nadal poprawna.

Inną zaletą tego rozwiązania jest to, że zmiana szybkości klatek oznaczałaby zmianę okresu tylko w TIM1. W przypadku nowoczesnych serw cyfrowych można zejść nawet do 200-300 Hz, ale jeśli chcesz dostroić, zapoznaj się z instrukcją obsługi serwomechanizmu.

Zalecana:

Licznik częstotliwości o wysokiej rozdzielczości: 5 kroków (ze zdjęciami)

Licznik częstotliwości o wysokiej rozdzielczości: Ta instrukcja pokazuje licznik częstotliwości odwrotności zdolny do szybkiego i rozsądnego pomiaru częstotliwości. Wykonany jest ze standardowych komponentów i można go zrobić w weekend (zajęło mi to trochę więcej czasu :-)) EDIT: Kod jest już dostępny

Kamera internetowa o wysokiej rozdzielczości: 9 kroków (ze zdjęciami)

Kamera internetowa o wysokiej rozdzielczości: Przez kilka lat korzystałem z kamery internetowej opartej na RPi (z modułem PiCam). Wyprodukowane obrazy były w porządku, ale potem nadszedł moment, w którym nie byłem już zadowolony z jakości. Postanowiłem zrobić kamerę internetową o wysokiej rozdzielczości. Następujące części zawierają

OpenLogger: wysokiej rozdzielczości, włączony Wi-Fi, open source, przenośny rejestrator danych: 7 kroków

OpenLogger: Przenośny rejestrator danych o wysokiej rozdzielczości, z obsługą Wi-Fi, Open Source: OpenLogger to przenośny rejestrator danych o otwartym kodzie źródłowym, tani i wysokiej rozdzielczości, zaprojektowany w celu zapewnienia wysokiej jakości pomiarów bez konieczności korzystania z drogiego oprogramowania lub oprogramowania do pisania od zera. Jeśli jesteś inżynierem, naukowcem lub entuzjastą, który

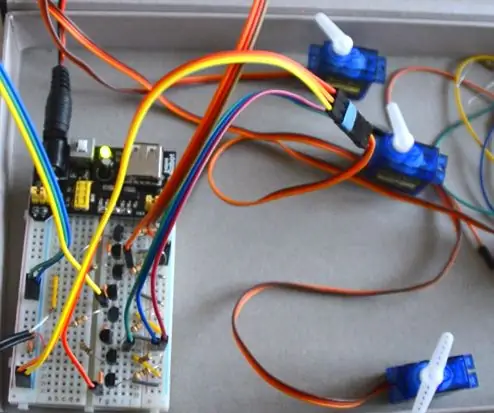

Kontroluj do 4 serwomechanizmów za pomocą smartfona lub dowolnego urządzenia z wyjściem audio: 3 kroki

Kontroluj do 4 serwomechanizmów za pomocą smartfona lub dowolnego urządzenia z wyjściem audio: Tutaj przedstawiam prosty montaż elektroniczny do sterowania maksymalnie czterema serwomechanizmami za pomocą dowolnego urządzenia, które może odczytać plik audio

Jak uzyskać obrazy o wysokiej rozdzielczości z instrukcji: 4 kroki

Jak uzyskać obrazy o wysokiej rozdzielczości z instrukcji: Czy naprawdę podobał ci się ten instruktażowy obraz i chcesz zapisać jego kopię w wysokiej rozdzielczości? Ta wspaniała mała funkcja jest łatwo przeoczona