Spisu treści:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:30.

- Ostatnio zmodyfikowany 2025-01-23 15:03.

W tej instrukcji zaprojektujemy od podstaw SPI Bus Master w VHDL.

Krok 1: Przegląd SPI

- SPI to synchroniczna magistrala szeregowa

- Jego popularność i prostota sprawiły, że stał się de facto standardem w komunikacji szeregowej

- Magistrala pełnodupleksowa

- Prosty protokół i jedna z najszybszych magistrali szeregowych

Krok 2: Specyfikacje projektowe

Oto specyfikacje SPI Master, które zaprojektujemy:

- Obsługuje wszystkie cztery tryby pracy; dynamicznie konfigurowalny

- Zegar umożliwia kontrolę w celu oszczędzania energii

- Statycznie konfigurowalna długość i szybkość słowa

- Pojedyncze przerwanie zarówno dla transmisji, jak i odbioru

Krok 3: Rozpoczęcie

Przede wszystkim nasz adres IP powinien mieć dwa interfejsy. Jeden to interfejs szeregowy, a drugi to interfejs równoległy. Interfejs szeregowy składa się ze standardowych sygnałów SPI: MOSI, MISO, SS, SCLK.

MOSI jest czasami nazywane SDO, a MISO jest czasami nazywane SDI.

Interfejs szeregowy służy do komunikacji z zewnętrznymi urządzeniami peryferyjnymi, tj. Slave SPI.

Interfejs równoległy służy do komunikacji z naszym hostem, tj. mikrokontrolerem lub mikroprocesorem, który faktycznie mówi Masterowi, jakie dane mają być przesyłane i odbierane szeregowo przez linie szeregowe. tj. Wszystkie magistrale danych należą do interfejsu równoległego.

Mamy zegar globalny, który steruje wewnętrzną logiką SPI, a także SCLK, który generujemy wewnętrznie.

Mamy również pewne sygnały sterujące, takie jak włączenie zapisu, włączenie zegara. Oraz przerwania i inne sygnały stanu.

Ponieważ mamy do czynienia ze złożonymi warunkami sterowania, łatwiej jest zaprojektować takie adresy IP komunikacji szeregowej jak FSM. Zaprojektujemy również master SPI jako FSM. FSM będzie sterowany przez inny zegar wewnętrzny, który jest dwukrotnym zegarem SCLK. Ten wewnętrzny zegar jest generowany przy użyciu synchronicznych liczników zegara globalnego.

Wszystkie sygnały sterujące, które przecinają domeny zegarowe, mają synchronizatory, aby były po bezpiecznej stronie.

Krok 4: Widok RTL rdzenia głównego SPI i przebiegów symulacji

Jest to czysta konstrukcja RTL bez dedykowanych adresów IP FPGA. Dlatego jest to w pełni przenośny kod do dowolnego układu FPGA.

Zalecana:

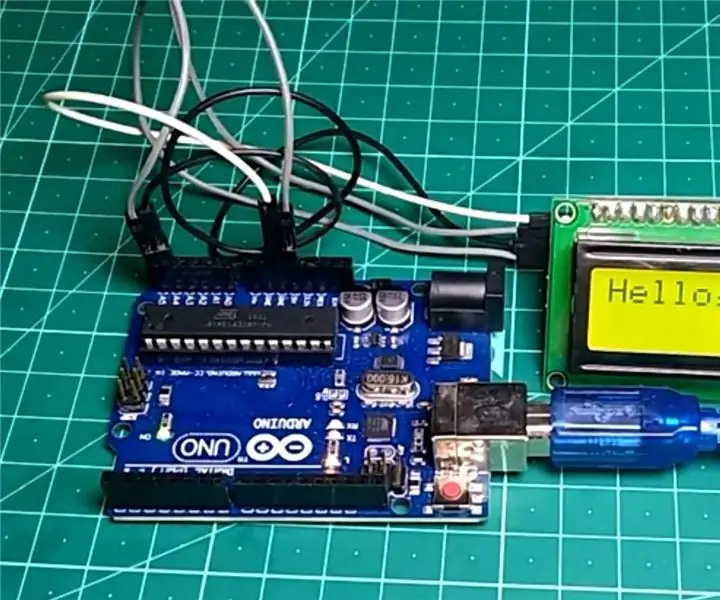

Wyświetlacz LCD I2C / IIC - Użyj SPI LCD do wyświetlacza LCD I2C za pomocą modułu SPI to IIC z Arduino: 5 kroków

Wyświetlacz LCD I2C / IIC | Użyj SPI LCD do wyświetlacza LCD I2C Używanie modułu SPI to IIC z Arduino: Cześć chłopaki, ponieważ normalny SPI LCD 1602 ma zbyt wiele przewodów do podłączenia, więc bardzo trudno jest połączyć go z arduino, ale na rynku dostępny jest jeden moduł, który może przekonwertuj wyświetlacz SPI na wyświetlacz IIC, więc musisz podłączyć tylko 4 przewody

Projekt I2C Master w VHDL: 5 kroków

Projekt Master I2C w VHDL: W tej instrukcji omawiamy projektowanie prostego mastera I2C w VHDL. UWAGA: kliknij każdy obraz, aby zobaczyć pełny obraz

Projekt prostego kontrolera VGA w VHDL i Verilog: 5 kroków

Projekt prostego kontrolera VGA w VHDL i Verilog: W tej instrukcji zaprojektujemy prosty kontroler VGA w RTL. Kontroler VGA to układ cyfrowy przeznaczony do sterowania wyświetlaczami VGA. Odczytuje z bufora ramki (pamięć VGA), który reprezentuje ramkę do wyświetlenia i generuje niezbędn

Projekt UART w VHDL: 5 kroków

Projekt UART w VHDL: UART to skrót od Universal Asynchronous Receiver Transmitter. Jest to najpopularniejszy i najprostszy protokół komunikacji szeregowej. W tej instrukcji dowiesz się, jak zaprojektować moduł UART w VHDL

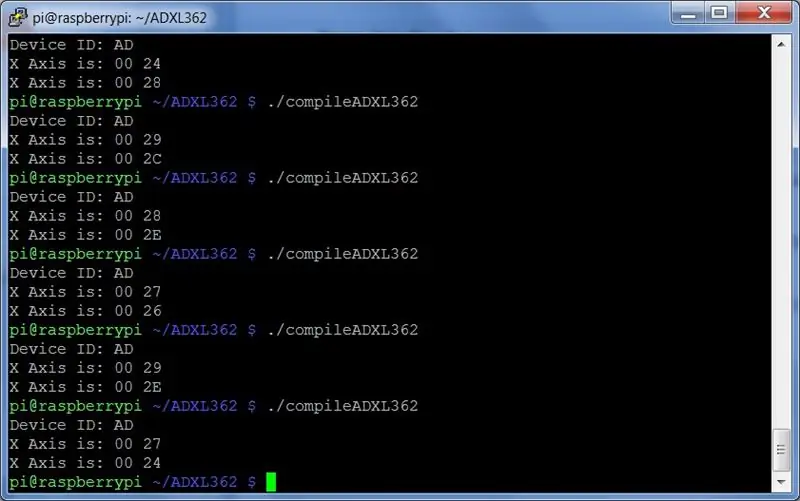

Wstępny* SPI na Pi: Komunikacja z 3-osiowym akcelerometrem SPI za pomocą Raspberry Pi: 10 kroków

Wstępny* SPI na Pi: Komunikacja z 3-osiowym akcelerometrem SPI Korzystanie z Raspberry Pi: Przewodnik krok po kroku, jak skonfigurować Raspbian i komunikować się z urządzeniem SPI za pomocą biblioteki SPI bcm2835 (NIE jest to bit banged!) bardzo wstępne… Muszę dodać lepsze zdjęcia fizycznego podłączenia i przepracować trochę niezręcznego kodu