Spisu treści:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:30.

- Ostatnio zmodyfikowany 2025-01-23 15:03.

W tej instrukcji zaprojektujemy prosty kontroler VGA w RTL. Kontroler VGA to układ cyfrowy przeznaczony do sterowania wyświetlaczami VGA. Odczytuje z bufora ramki (pamięci VGA), który reprezentuje ramkę do wyświetlenia i generuje niezbędne dane oraz sygnały synchronizacji do celów wyświetlania.

Jeśli szukasz kodu Verilog/System verilog: Odwiedź mój blog Kontroler VGA i system wideo w Verilog

Krok 1: Interfejs kontrolera VGA

Poniżej przedstawiono główne sygnały interfejsu w kontrolerze VGA

- Zegar pikseli lub zegar VGA

- Sygnały HSYNC i VSYNC

Dla wybranego wyświetlacza VGA, musisz najpierw obliczyć częstotliwość zegara pikseli potrzebną do jego napędzania. Zależy to od 3 parametrów: Całkowita liczba pikseli w poziomie, Całkowita liczba pikseli w pionie, Częstotliwość odświeżania ekranu.

Zazwyczaj F = THP * TVP * Częstotliwość odświeżania

Znajdź dokumentację dotyczącą zegara pikselowego potrzebną do różnych wyświetlaczy VGA w załączonym pliku RAR.

Sygnały HSYNC i VSYNC są generowane z zegara Pixel. Taktowanie sygnałów HSYNC i VSYNC zależy od liczby parametrów: pozioma i pionowa przednia, pozioma i pionowa tylna, pozioma i pionowa liczba wyświetlanych pikseli, pozioma i pionowa szerokość impulsów synchronizacji i polaryzacja.

Parametry te są standaryzowane dla wybranego wyświetlacza VGA. Znajdź te dokumenty w załączonym RAR.

Te parametry są konfigurowalnymi parametrami w naszym IP kontrolera VGA.

Krok 2: Integracja kontrolera VGA z wyświetlaczem VGA

Rysunek pokazuje, jak zintegrować kontroler VGA z wyświetlaczem VGA. Do skompletowania systemu potrzebne są jeszcze dwa komponenty:

- Bufor ramki: Pamięć przechowująca ramkę do wyświetlenia.

- Video DAC: DAC, który konwertuje dane cyfrowe RGB i steruje wyświetlaczem VGA sygnałami analogowymi RGB o odpowiednim poziomie napięcia.

Jednym z najprostszych i najpopularniejszych przetworników DAC wideo jest ADV7125. Jest to 8-bitowy przetwornik cyfrowo-analogowy, który konwertuje cyfrowe słowa RGB na sygnały analogowe 0-0,7 V i steruje wyświetlaczem VGA.

Krok 3: Projekt bufora ramki

To właśnie pamięć „przechowuje” obraz, który ma być wyświetlony. Jest to zazwyczaj pamięć RAM lub czasami ROM. Omówimy, jak zaprojektować bufor ramki do reprezentowania obrazu. Bufor ramki przekazuje te cyfrowe informacje do Video DAC na polecenie kontrolera VGA.

Najpierw musimy określić potrzebną głębię pikseli. Decyduje o jakości obrazu, różnorodności kolorów, jakie może reprezentować piksel. W przypadku 8-bitowego przetwornika cyfrowo-analogowego musimy reprezentować składowe koloru podstawowego piksela: R, G i B w 8 bitach każdy. Oznacza to, że piksel jest 24-bitowy.

Każdy piksel jest przechowywany w sposób ciągły w lokalizacjach pamięci bufora ramki.

Załóżmy, że obraz do wyświetlenia ma 800x600 pikseli.

Dlatego potrzebny bufor ramki to 800x600 = 480000 x 24 bity pamięci

Całkowity rozmiar pamięci to 800x600x24 = 1400 kB ok.

Jeśli obraz czarno-biały, 800x600x1 = ok. 60 kB.

Blokowe pamięci RAM mogą być używane do reprezentowania bufora ramki w układach FPGA Xilinx.

Krok 4: Uwagi

- Dodatkowe sygnały są potrzebne na kontrolerze VGA w zależności od wybranego DAC. Użyłem ADV7125.

- Dodaj opóźnienia cyklu przez przerzutniki na VSYNC i HSYNC przed uruchomieniem wyświetlacza VGA. Dzieje się tak z powodu opóźnień DAC i pamięci. Sygnały pikseli powinny być zsynchronizowane z HSYNC i VSYNC. W moim przypadku było to opóźnienie 2 cykli.

- Jeśli bufor ramki o danym rozmiarze nie może być zaprojektowany na FPGA z powodu ograniczenia rozmiaru pamięci RAM, użyj mniejszej pamięci do reprezentowania obrazu i po prostu edytuj kod, aby przesunąć adres na granicy dostępnej pamięci, a nie na granicy pełnej ramki. Spowoduje to powtarzanie tego samego obrazu na całym ekranie. Inną metodą jest skalowanie pikseli, w którym każdy piksel jest replikowany, aby pokazać cały obraz na pełnym ekranie, w mniejszej rozdzielczości. Można to zrobić, dostosowując logikę inkrementacji adresu w kodzie.

- IP jest w pełni przenośny we wszystkich układach FPGA i jest weryfikowany taktowaniem do 100 MHz na FPGA Virtex-4.

Krok 5: Załączone pliki

RAR zawiera:

- Kod kontrolera VGA

- Pliki PDF ze standardami VGA.

Zalecana:

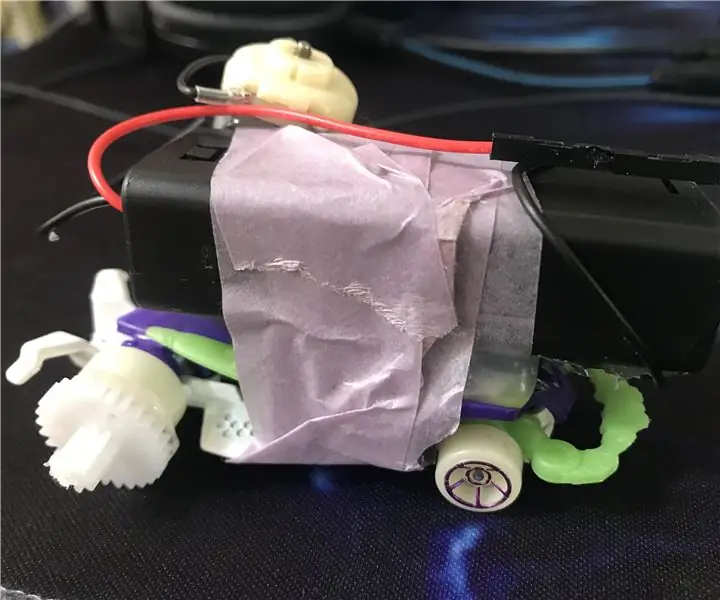

Tworzenie prostego robota z rzeczy, które możesz znaleźć w swoim domu (wersja hotwheel): 5 kroków

Tworzenie prostego robota z rzeczy, które możesz znaleźć w swoim domu (wersja hotwheel): Ten instruktaż pokaże ci, jak zrobić hotwheel, który działa sam i działa na bateriach podwójnego A. Będziesz musiał używać tylko rzeczy, które najprawdopodobniej znajdziesz w swoim domu. Należy pamiętać, że ten robot prawdopodobnie nie będzie szedł dokładnie prosto, a

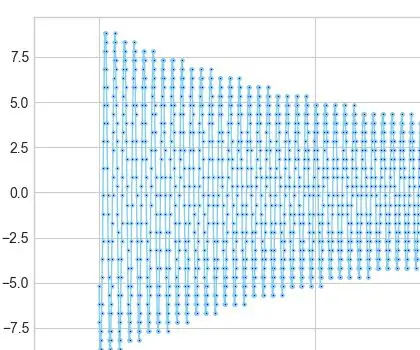

Eksperymentalne badanie prostego ruchu harmonicznego: 5 kroków

Eksperymentalne badanie prostego ruchu harmonicznego: W klasie często używamy stopera do przeprowadzenia eksperymentu z wahadłem lub prostego eksperymentu z ruchem harmonicznym. Oto wyzwanie, czy możemy stworzyć prawdziwy wykres jego ruchu i zobaczyć, jaka jest chwilowa pozycja kątowa i prędkość

Projekt prostego czterokierunkowego asocjacyjnego kontrolera pamięci podręcznej w VHDL: 4 kroki

Projekt prostego czterokierunkowego skojarzonego kontrolera pamięci podręcznej w VHDL: W mojej poprzedniej instrukcji widzieliśmy, jak zaprojektować prosty, bezpośrednio mapowany kontroler pamięci podręcznej. Tym razem idziemy o krok do przodu. Będziemy projektować prosty czterokierunkowy kontroler asocjacyjnej pamięci podręcznej. Korzyść ? Mniej chybień, ale kosztem wydajności

Projekt programowalnego kontrolera przerwań w VHDL: 4 kroki

Projekt programowalnego kontrolera przerwań w VHDL: Jestem przytłoczony rodzajem odpowiedzi, które otrzymuję na tym blogu. Dziękuję chłopakom za odwiedzenie mojego bloga i zmotywowanie mnie do dzielenia się z wami moją wiedzą. Tym razem przedstawię projekt kolejnego interesującego modułu, który widzimy we wszystkich SOC-ach -- Przerwanie C

Projekt prostego kontrolera pamięci podręcznej w VHDL: 4 kroki

Projekt prostego kontrolera pamięci podręcznej w VHDL: Piszę tę instrukcję, ponieważ trochę trudno mi było uzyskać referencyjny kod VHDL do nauczenia się i rozpoczęcia projektowania kontrolera pamięci podręcznej. Więc sam zaprojektowałem kontroler pamięci podręcznej od podstaw i przetestowałem go z powodzeniem na FPGA. mam p