Spisu treści:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:29.

- Ostatnio zmodyfikowany 2025-06-01 06:10.

Jestem przytłoczony odpowiedziami, jakie otrzymuję na tym blogu. Dziękuję chłopakom za odwiedzenie mojego bloga i zmotywowanie mnie do dzielenia się z wami moją wiedzą. Tym razem przedstawię projekt kolejnego interesującego modułu, który widzimy we wszystkich SOC-ach - Interrupt Controller.

Będziemy projektować prosty, ale potężny programowalny kontroler przerwań. Jest to w pełni konfigurowalny i sparametryzowany projekt, który można przenosić na różne platformy. Zaprojektowałem to po przeczytaniu wielu popularnych architektur kontrolerów przerwań, takich jak NVIC, 8259a, RISC-V PLIC, Microblaze's INTC itp. Mam nadzieję, że ten blog okaże się pomocny i pomoże ci poznać sposób obsługi przerwań przez procesor za pomocą kontrolera przerwań.

Krok 1: Specyfikacje

Poniżej znajdują się specyfikacje IP:

- Interfejs AHB3-Lite.

-

Parametry konfigurowalne statycznie:

- Liczba zewnętrznych źródeł przerwań; obsługuje do 63 przerwań.

- liczba poziomów priorytetowych; obsługuje do 63 poziomów.

- Liczba poziomów zagnieżdżenia; obsługuje do 8 poziomów zagnieżdżania.

- Szerokość busa; 32 lub 64.

- Przerwania maskowalne globalnie i lokalnie.

- Dynamicznie konfigurowalny poziom priorytetu dla każdego przerwania.

- Dwa tryby pracy - tryb w pełni zagnieżdżony i tryb z równym priorytetem.

- Obsługuje aktywne przerwania wrażliwe na wysoki poziom.

W projekcie zastosowano mechanizm uzgadniania przerwań inspirowany specyfikacją RISC-V PLIC.

Wywłaszczanie przerwań inspirowane jest 8259a

Inne czyta: Microblaze INTC, NVIC

Krok 2: Przegląd PIC

Programowalny kontroler przerwań (PIC) odbiera wiele przerwań z zewnętrznych urządzeń peryferyjnych i łączy je w jedno wyjście przerwania do rdzenia procesora docelowego.

PIC jest kontrolowany przez rejestry kontrolne i statusowe. Wszystkie rejestry PIC są mapowane w pamięci i dostępne przez interfejs magistrali AHB3-Lite.

Bank rejestrów składa się z rejestrów konfiguracyjnych, rejestrów załączających, rejestrów oczekujących, rejestrów eksploatacji, rejestrów priorytetowych oraz rejestrów ID, które są typowe dla kontrolerów przerwań.

Rejestr konfiguracji służy do ustawienia trybu pracy PIC. Może pracować w trybie w pełni zagnieżdżonym lub w trybie równego priorytetu.

Każdemu przerwaniu można przypisać priorytety i indywidualnie maskować. Obsługiwane jest również globalne maskowanie wszystkich przerwań.

Bank rejestrów wchodzi w interakcję z Priority Resolver i BTC (Binary-Tree-Comparator), aby rozwiązać priorytety oczekujących przerwań i odpowiednio dostarczyć przerwanie do procesora. Rejestr ID zawiera ID oczekującego przerwania o najwyższym priorytecie.

Krok 3: Projekt i wdrożenie RTL

Projekt PIC kładzie nacisk na zmniejszenie opóźnień w rozwiązywaniu priorytetów, co jest najbardziej krytyczną czasowo częścią projektu. Ponieważ projekt rozwiązuje priorytety w jednym cyklu zegara, wydajność spada wraz ze wzrostem liczby źródeł o złożoności Log2.

Projekt został pomyślnie wdrożony i zweryfikowany taktowanie do następujących częstotliwości w FPGA Artix-7.

- Do 15 źródeł: 100 MHz

- Do 63 źródeł: 50 MHz

Opóźnienie przerwania dodane przez sam PIC to 3 cykle zegara (z wyłączeniem czasu przełączania kontekstu procesora i czasu pobrania pierwszej instrukcji ISR).

Krok 4: Ważne uwagi i załączone pliki

Ważne notatki:

- Jeśli interfejs AHB3-Lite jest niepożądany, możesz zmienić górny moduł i użyć szkieletowej konstrukcji PIC. Jednak dostarczone stanowisko testowe jest przeznaczone dla IP z interfejsem AHB3-Lite.

- PIC IP v1.0 to całkowicie przenośny, czysty projekt RTL.

- Sprawdzony funkcjonalnie do pracy w obu trybach.

Załączone pliki:

- Kody projektowe i testbench w VHDL.

- Pełna dokumentacja IP.

Jest to projekt open-source… Zapraszam do korzystania…

W przypadku jakichkolwiek pytań, w dowolnym momencie:

Mitu Raj

Zalecana:

Laboratorium przerwań (praca w toku): 3 kroki

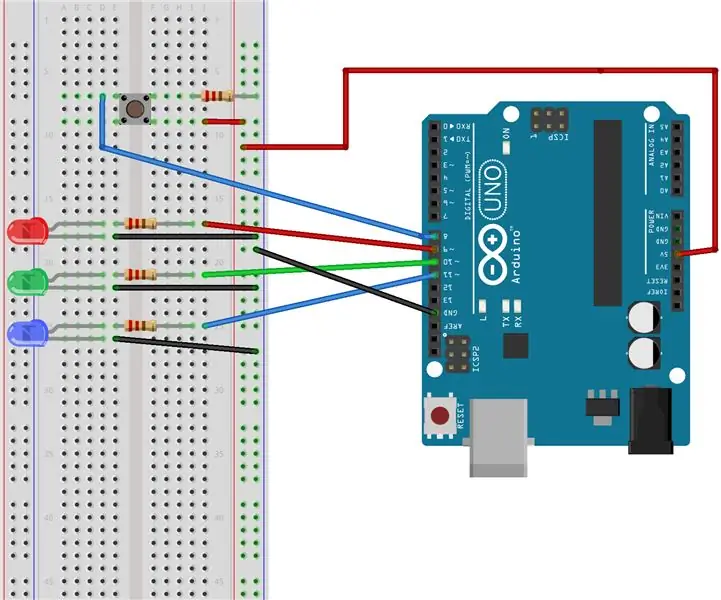

Laboratorium przerwań (praca w toku): Celem tego laboratorium jest uruchomienie programu Arduino przy użyciu przerwań. To laboratorium nie działa w pełni poprawnie z powodu problemów z kodowaniem. Czego będziesz potrzebować: - 1 Arduino Uno - 1 płytka prototypowa - 1 przycisk - 3 diody LED - Rezystory 220 Ohm - Przewody połączeniowe

Projekt prostego czterokierunkowego asocjacyjnego kontrolera pamięci podręcznej w VHDL: 4 kroki

Projekt prostego czterokierunkowego skojarzonego kontrolera pamięci podręcznej w VHDL: W mojej poprzedniej instrukcji widzieliśmy, jak zaprojektować prosty, bezpośrednio mapowany kontroler pamięci podręcznej. Tym razem idziemy o krok do przodu. Będziemy projektować prosty czterokierunkowy kontroler asocjacyjnej pamięci podręcznej. Korzyść ? Mniej chybień, ale kosztem wydajności

Projekt prostego kontrolera pamięci podręcznej w VHDL: 4 kroki

Projekt prostego kontrolera pamięci podręcznej w VHDL: Piszę tę instrukcję, ponieważ trochę trudno mi było uzyskać referencyjny kod VHDL do nauczenia się i rozpoczęcia projektowania kontrolera pamięci podręcznej. Więc sam zaprojektowałem kontroler pamięci podręcznej od podstaw i przetestowałem go z powodzeniem na FPGA. mam p

Projekt prostego kontrolera VGA w VHDL i Verilog: 5 kroków

Projekt prostego kontrolera VGA w VHDL i Verilog: W tej instrukcji zaprojektujemy prosty kontroler VGA w RTL. Kontroler VGA to układ cyfrowy przeznaczony do sterowania wyświetlaczami VGA. Odczytuje z bufora ramki (pamięć VGA), który reprezentuje ramkę do wyświetlenia i generuje niezbędn

Wprowadzenie i samouczek dotyczący programowalnego zasilacza!: 7 kroków

Wprowadzenie i samouczek dotyczący programowalnego zasilacza!: Jeśli kiedykolwiek zastanawiałeś się nad programowalnymi zasilaczami, musisz przejść przez tę instrukcję, aby uzyskać pełną wiedzę i amp; praktyczny przykład zasilacza programowalnego. Również osoby zainteresowane elektroniką prosimy o zapoznanie się z