Spisu treści:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:29.

- Ostatnio zmodyfikowany 2025-01-23 15:03.

Piszę tę instrukcję, ponieważ trochę trudno było mi uzyskać jakiś referencyjny kod VHDL do nauczenia się i rozpoczęcia projektowania kontrolera pamięci podręcznej. Więc sam zaprojektowałem kontroler pamięci podręcznej od podstaw i przetestowałem go z powodzeniem na FPGA. Przedstawiłem tutaj prosty, bezpośrednio mapowany kontroler pamięci podręcznej, a także modelowałem cały system procesor-pamięć do testowania kontrolera pamięci podręcznej. Mam nadzieję, że uznacie to za przydatne jako odniesienie do projektowania własnych kontrolerów pamięci podręcznej.

Krok 1: Specyfikacje

Oto główne specyfikacje kontrolera pamięci podręcznej, który zamierzamy zaprojektować:

- Bezpośrednio mapowane. (przejdź do tego linku, jeśli szukasz asocjacyjnego mapowanego kontrolera pamięci podręcznej)

- Jednobankowa, blokująca pamięć podręczna.

- Zasady zapisu dotyczące trafień związanych z zapisem.

- Zasady alokacji lub zapisywania z pominięciem zapisu w przypadku chybionych zapisów.

- Brak bufora zapisu lub innych optymalizacji.

- Tablica tagów jest włączona.

Poza tym zaprojektujemy również pamięć podręczną i system pamięci głównej.

Domyślne (konfigurowalne) specyfikacje pamięci podręcznej:

- 256 bajtów pamięci podręcznej z jednym bankiem.

- 16 linii pamięci podręcznej, każda linia pamięci podręcznej (blok) = 16 bajtów.

Specyfikacje pamięci głównej:

- Synchroniczna pamięć odczytu/zapisu.

- Wielobankowa pamięć z przeplotem - cztery banki pamięci.

- Każdy rozmiar banku = 1 kB każdy. Stąd całkowity rozmiar = 4 kB.

- Pamięć adresowalna Word (4 bajty) z 10-bitową magistralą adresową.

- Większa przepustowość do odczytu. Szerokość odczytu danych = 16 bajtów w jednym cyklu zegara.

- Szerokość danych zapisu = 4 bajty.

UWAGA: sprawdź moje nowsze instrukcje, jeśli szukasz 4-kierunkowego asocjacyjnego kontrolera pamięci podręcznej

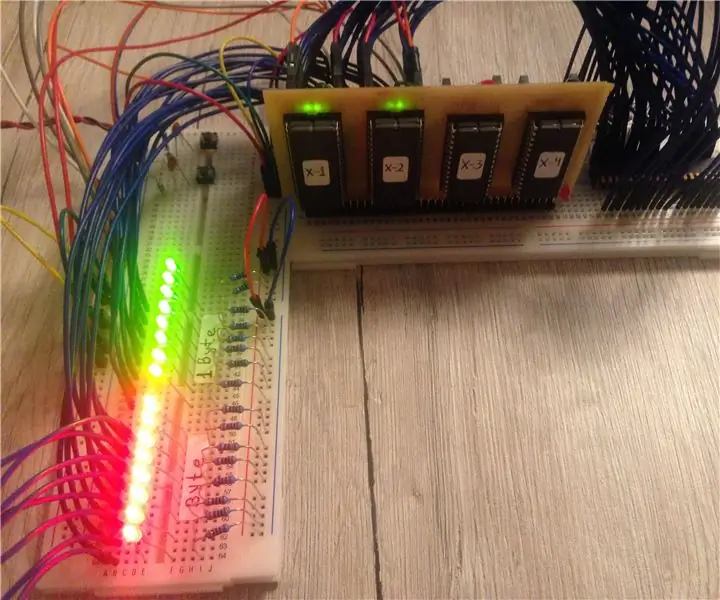

Krok 2: Widok RTL całego systemu

Pełna reprezentacja RTL modułu górnego jest pokazana na rysunku (bez procesora). Domyślne specyfikacje autobusów to:

- Wszystkie magistrale danych są magistralami 32-bitowymi.

- Szyna adresowa = Szyna 32-bitowa (ale tylko 10 bitów jest tutaj adresowanych przez pamięć).

- Blok danych = 128 bitów (szyna szerokopasmowa do odczytu).

- Wszystkie komponenty są sterowane tym samym zegarem.

Krok 3: Środowisko testowe

Top Module został przetestowany na stanowisku testowym, które po prostu modeluje procesor bez potoku (ponieważ zaprojektowanie całego procesora wcale nie jest łatwe !!). Stanowisko testowe często generuje żądania odczytu/zapisu danych do pamięci. To kpi z typowych instrukcji „Load” i „Store”, wspólnych dla wszystkich programów wykonywanych przez procesor. Wyniki testów pomyślnie zweryfikowały funkcjonalność kontrolera pamięci podręcznej. Poniżej znajdują się zaobserwowane statystyki testu:

- Wszystkie sygnały odczytu/zapisu chybienia i trafienia zostały wygenerowane poprawnie.

- Wszystkie operacje odczytu/zapisu danych zakończyły się pomyślnie.

- Nie wykryto problemów z niespójnością/niespójnością danych.

- Projekt został pomyślnie zweryfikowany w czasie dla Maxm. Częstotliwość taktowania = 110 MHz w płytce Xilinx Virtex-4 ML-403 (cały system), 195 MHz dla samego Cache Controllera.

- Dla pamięci głównej wywnioskowano blokowe pamięci RAM. Wszystkie inne macierze zostały zaimplementowane na LUT.

Krok 4: Załączone pliki

Do tego bloga dołączone są następujące pliki:

- Pliki. VHD kontrolera pamięci podręcznej, tablicy danych pamięci podręcznej, głównego systemu pamięci.

- Stanowisko testowe.

- Dokumentacja kontrolera pamięci podręcznej.

Uwagi:

- Przejrzyj dokumentację, aby w pełni zrozumieć specyfikacje kontrolera pamięci podręcznej przedstawione tutaj.

- Wszelkie zmiany w kodzie są zależne od innych modułów. Tak więc zmiany powinny być dokonywane rozsądnie. Zwróć uwagę na wszystkie komentarze i nagłówki, które podałem.

- Jeśli z jakiegoś powodu blokowe pamięci RAM nie są wywnioskowane dla pamięci głównej, ZREDUKUJ rozmiar pamięci, a następnie zmiany szerokości szyn adresowych w plikach i tak dalej. Aby ta sama pamięć mogła być zaimplementowana na LUT lub rozproszonej pamięci RAM. Oszczędzi to czas i zasoby routingu. Lub przejdź do odpowiedniej dokumentacji FPGA i znajdź kompatybilny kod dla bloku RAM i odpowiednio go edytuj, używając tych samych specyfikacji szerokości magistrali adresowej. Ta sama technika dla FPGA Altera.

Zalecana:

Projekt prostego czterokierunkowego asocjacyjnego kontrolera pamięci podręcznej w VHDL: 4 kroki

Projekt prostego czterokierunkowego skojarzonego kontrolera pamięci podręcznej w VHDL: W mojej poprzedniej instrukcji widzieliśmy, jak zaprojektować prosty, bezpośrednio mapowany kontroler pamięci podręcznej. Tym razem idziemy o krok do przodu. Będziemy projektować prosty czterokierunkowy kontroler asocjacyjnej pamięci podręcznej. Korzyść ? Mniej chybień, ale kosztem wydajności

Projekt programowalnego kontrolera przerwań w VHDL: 4 kroki

Projekt programowalnego kontrolera przerwań w VHDL: Jestem przytłoczony rodzajem odpowiedzi, które otrzymuję na tym blogu. Dziękuję chłopakom za odwiedzenie mojego bloga i zmotywowanie mnie do dzielenia się z wami moją wiedzą. Tym razem przedstawię projekt kolejnego interesującego modułu, który widzimy we wszystkich SOC-ach -- Przerwanie C

Jak zrobić prostego Spiderbota na Halloween: 4 kroki (ze zdjęciami)

Jak zrobić prostego Spiderbota na Halloween: Jest to prosty, zabawny Bristlebot na Halloween! Bristleboty to świetne projekty startowe dla osób uczących się podstaw obwodów i budowy robotów. Używając główki szczoteczki do zębów do ciała, małego silnika zapewniającego ruch i baterii

Projekt prostego kontrolera VGA w VHDL i Verilog: 5 kroków

Projekt prostego kontrolera VGA w VHDL i Verilog: W tej instrukcji zaprojektujemy prosty kontroler VGA w RTL. Kontroler VGA to układ cyfrowy przeznaczony do sterowania wyświetlaczami VGA. Odczytuje z bufora ramki (pamięć VGA), który reprezentuje ramkę do wyświetlenia i generuje niezbędn

Karta pamięci wykonana z pamięci CMOS EPROM: 6 kroków (ze zdjęciami)

Karta pamięci wykonana z CMOS EPROM: Instrukcja stworzona przeze mnie pomoże Ci zbudować ogromną pojemność pamięci, która przyda się do wielu projektów i pomiarów. Karta pamięci nadaje się do wielokrotnego użytku i może być znacznie bardziej realiable w porównaniu z kartami flash i innymi