Spisu treści:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:30.

- Ostatnio zmodyfikowany 2025-06-01 06:10.

W tej instrukcji omówiono projektowanie prostego mastera I2C w VHDL.

UWAGA: kliknij na każdy obraz, aby zobaczyć pełny obraz

Krok 1: Przegląd magistrali I2C

•Stojaki pod układ scalony Inter.

•Synchroniczny, półdupleks.

• Interfejs dwuprzewodowy - SDA i SCL.

•SDA - Szeregowa linia danych kontrolowana przez Master i Slave

•SCL - Zegar szeregowy generowany przez Master

• Protokół Multi-master, Multi-slave.

•Dwa tryby - 100 kbit/s i 400 kbit/s: wolny i szybki.

Krok 2: Projekt RTL w VHDL

Specyfikacja projektu naszego I2C Master

- 8-bitowa ramka danych.

- Tylko sterowanie jednokierunkowe SCL.

- 7-bitowy adres slave.

- Obsługuje zarówno wolne, jak i szybkie tryby.

- Pojedynczy master, multi-slave.

- Zgodny z oryginalną specyfikacją I2C firmy Philips.

Używany jest czysty kod RTL. Dzięki temu IP można łatwo przenosić we wszystkich układach FPGA. Kompaktowa konstrukcja oparta na FSM wykorzystująca wewnętrznie generowany zegar zapewnia optymalną powierzchnię i wydajność.

Krok 3: Symulacja i testowanie

Środowisko testowe

- Symulacja funkcjonalna i testowanie przy użyciu I2C Slave IP innej firmy.

- Zsyntetyzowany przy użyciu zestawu narzędzi Xilinx Vivado.

- Zaimplementowany i przetestowany na płytce Artix-7 FPGA.

- Zweryfikowany czasowo projekt dla 100 MHz.

- Przetestowane przebiegi na DSO/CRO.

- Pomyślnie przetestowano komunikację z Arduino UNO jako I2C Slave.

Krok 4: Ważne uwagi

- Podczas testowania Master przy użyciu I2C Slave IP, skonfiguruj kod Slave zgodnie z własnymi wymaganiami. Możesz zmienić domyślną częstotliwość zegara i adres urządzenia podrzędnego. Częstotliwość zegara powinna być również skonfigurowana w kodzie Master.

- Podczas testowania na pokładzie nie zapomnij o rezystorach podciągających, ponieważ linia SDA jest wspólnym wyjściem drenażu !!! Sprawdź w google zalecany rezystor podciągający dla różnych prędkości i2c. Użyłem 2.2K dla 100 kHz.

- Jeśli nie używasz stanowiska testowego i nie symulujesz urządzenia Master, ostrożnie symuluj sygnał SDA, ponieważ jest to sygnał dwukierunkowy (wejście). Ma dwa sterowniki, stronę master i stronę slave. Powinieneś wiedzieć, kiedy „wymusić”, a kiedy „odmusić”.

- SCL to linia jednokierunkowa. Nie ma potrzeby podciągania się.

- Proszę dokładnie zapoznać się z dokumentacją IP.

Krok 5: Załączone pliki

- Wszystkie kody RTL I2C Master.

- Stanowisko testowe, kody I2C Slave również do testowania.

- Dokumentacja IP.

W przypadku jakichkolwiek pytań zapraszam do kontaktu:

Mitu Raj

śledź mnie:

W przypadku pytań prosimy o kontakt: iammituraj@gmail.com

Zalecana:

Projekt prostego czterokierunkowego asocjacyjnego kontrolera pamięci podręcznej w VHDL: 4 kroki

Projekt prostego czterokierunkowego skojarzonego kontrolera pamięci podręcznej w VHDL: W mojej poprzedniej instrukcji widzieliśmy, jak zaprojektować prosty, bezpośrednio mapowany kontroler pamięci podręcznej. Tym razem idziemy o krok do przodu. Będziemy projektować prosty czterokierunkowy kontroler asocjacyjnej pamięci podręcznej. Korzyść ? Mniej chybień, ale kosztem wydajności

Projekt prostego kontrolera VGA w VHDL i Verilog: 5 kroków

Projekt prostego kontrolera VGA w VHDL i Verilog: W tej instrukcji zaprojektujemy prosty kontroler VGA w RTL. Kontroler VGA to układ cyfrowy przeznaczony do sterowania wyświetlaczami VGA. Odczytuje z bufora ramki (pamięć VGA), który reprezentuje ramkę do wyświetlenia i generuje niezbędn

Projekt SPI Master w VHDL: 6 kroków

Projekt SPI Master w VHDL: W tej instrukcji zaprojektujemy od podstaw SPI Bus Master w VHDL

Projekt UART w VHDL: 5 kroków

Projekt UART w VHDL: UART to skrót od Universal Asynchronous Receiver Transmitter. Jest to najpopularniejszy i najprostszy protokół komunikacji szeregowej. W tej instrukcji dowiesz się, jak zaprojektować moduł UART w VHDL

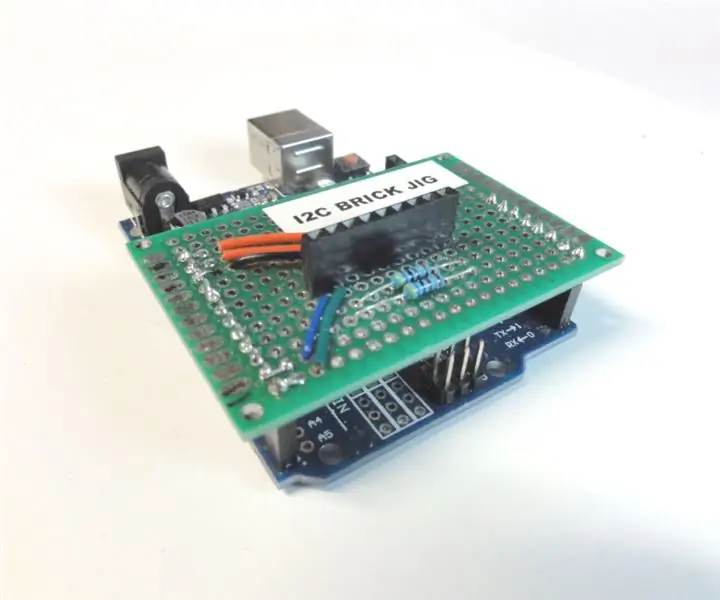

IOT123 - I2C BRICK MASTER JIG: 4 kroki

IOT123 - I2C BRICK MASTER JIG: Podczas opracowywania ASSIMILATE SENSORS i ACTORS mam pod ręką UNO do wysyłania adhoc poleceń I2C do opracowywanych prototypów. Jedną z zalet I2C BRICKS są znormalizowane pinouty. Zamiast używać za każdym razem przewodów płytki stykowej