Spisu treści:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:31.

- Ostatnio zmodyfikowany 2025-01-23 15:03.

Celem tego projektu jest stworzenie funkcji wyświetlania obrazu Smart Mirror. Lustro może wyświetlać prognozy (słonecznie, częściowo słonecznie, pochmurno, wietrznie, deszcz, grzmoty i śnieg) oraz wartości temperatury od -9999° do 9999°. Wartości prognozy i temperatury są zakodowane na sztywno, tak jak gdyby emulowały je analizowane z API pogodowego.

Projekt wykorzystuje płytę Zynq-Zybo-7000 z systemem FreeRTOS i Vivado 2018.2 do projektowania i programowania sprzętu.

Części:

Zynq-Zybo-7000 (z FreeRTOS)

19 LCD (640x480)

Kabel VGA

Lustro akrylowe 12 "x 18"

Krok 1: Konfiguracja Vivado

Pobierz Vivado 2018.2 z Xilinx i skorzystaj z licencji Webpack. Uruchom Vivado i „Utwórz nowy projekt” i nadaj mu nazwę. Następnie wybierz „Projekt RTL” i zaznacz „Nie określaj obecnie źródeł”. Wybierając część, wybierz „xc7z010clg400-1” i naciśnij „Zakończ” na następnej stronie.

Krok 2: Pakowanie adresu IP sterownika VGA

Dodaj plik vga_driver.sv do źródeł projektu. Następnie kliknij „Narzędzia” i wybierz „Utwórz i spakuj nowy adres IP”. Wybierz „Spakuj swój bieżący projekt”. Następnie wybierz lokalizację IP i „Dołącz pliki.xci”. Kliknij „OK” w wyskakującym okienku, a następnie „Zakończ”.

W „Kroki pakowania” przejdź do „Przegląd i pakiet” i wybierz „IP pakietu”.

Teraz vga_driver powinien być dostępny jako blok IP.

Krok 3: IP Zynq

W sekcji „Integrator IP” wybierz „Utwórz projekt blokowy”. Dodaj „System przetwarzania ZYNQ7” i kliknij dwukrotnie blok. Kliknij „Importuj ustawienia XPS” i prześlij plik ZYBO_zynq_def.xml.

Następnie w sekcji „Konfiguracja PS-PL” otwórz menu „AXI Non Secure Enablement” i zaznacz „Interfejs M AXI GP0”.

Następnie w sekcji „Konfiguracja MIO” otwórz menu rozwijane „Application Processor Unit” i zaznacz „Timer 0” i „Watchdog”.

Na koniec, w "Clock Configuration" otwórz menu "PL Fabric Clocks" i zaznacz "FCLK_CLK0" i przy 100 MHz.

Krok 4: IP GPIO

Dodaj dwa bloki GPIO do projektu blokowego. GPIO będą używane do kontrolowania adresu piksela i składowych RGB pikseli. Skonfiguruj bloki tak, jak pokazano na powyższych obrazkach. Po dodaniu i skonfigurowaniu obu bloków kliknij „Uruchom automatyzację połączeń”.

GPIO 0 - Kanał 1 kontroluje adres piksela, a Kanał 2 kontroluje kolor czerwony.

GPIO 1 - Kanał 1 kontroluje kolor zielony, a Kanał 2 kontroluje kolor niebieski.

Krok 5: Zablokuj pamięć

Dodaj adres IP generatora pamięci bloku do projektu bloku i skonfiguruj, jak pokazano powyżej. Kolory pikseli są zapisywane w adresach pamięci, które są następnie odczytywane przez sterownik VGA. Linia adresowa musi odpowiadać ilości używanych pikseli, więc musi mieć 16 bitów. Dane są również 16 bitowe, ponieważ jest 16 bitów koloru. Nie obchodzi nas czytanie jakichkolwiek bitów potwierdzających.

Krok 6: Inne IP

Załączony plik pdf przedstawia ukończony Projekt Bloku. Dodaj brakujący adres IP i zakończ połączenia. Również "Make Externals" dla kolorowych wyjść VGA oraz wyjść synchronizacji pionowej i poziomej.

xlconcat_0 - łączy poszczególne kolory w jeden 16-bitowy sygnał RGB, który jest podawany do pamięci RAM bloku.

xlconcat_1 - Łączy sygnały kolumn i wierszy ze sterownika VGA i jest podawany do portu B bloku RAM. Umożliwia to sterownikowi VGA odczytywanie wartości kolorów pikseli.

VDD - Stałe WYSOKIE połączone z zezwoleniem na zapis w bloku RAM, dzięki czemu zawsze możemy się do niego dostać.

xlslice_0, 1, 2 - Plasterki są używane do dzielenia sygnału RGB na pojedyncze sygnały R, G i B, które można podać do sterownika VGA.

Po zakończeniu projektowania bloku wygeneruj opakowanie HDL i dodaj plik ograniczeń.

*Block Design jest oparty na samouczku napisanym przez benlin1994*

Krok 7: SDK

Kod, który uruchamia ten projekt blokowy, znajduje się poniżej. Init.c zawiera funkcje obsługujące rysunek (prognozy, liczby, symbole stopni itp.). Główna pętla w main.c jest uruchamiana, gdy płyta jest zaprogramowana. Ta pętla ustawia wartości prognozy i temperatury, a następnie wywołuje funkcje rysowania w init.c. Obecnie przegląda wszystkie siedem prognoz i wyświetla jedną po drugiej. Zaleca się dodanie punktu przerwania w wierszu 239, aby można było zobaczyć każdy obraz. Kod jest skomentowany i da ci więcej informacji.

Krok 8: Wniosek

Aby ulepszyć obecny projekt, można wstępnie wczytać obrazy prognozy w postaci plików COE do generatorów pamięci bloków. Więc zamiast ręcznie rysować prognozy, jak to zrobiliśmy w kodzie C, można by wczytać obrazy. Próbowaliśmy to zrobić, ale nie mogliśmy tego uruchomić. Udało nam się odczytać wartości pikseli i wyprowadzić je, ale stworzyliśmy niechlujne obrazy, które w niczym nie przypominały tych, które wrzuciliśmy do pamięci RAM. Arkusz danych Generatora pamięci bloków jest przydatny do przeczytania.

Projekt jest zasadniczo połową Smart Mirror, ponieważ brakuje w nim aspektu łączności internetowej. Dodanie tego dałoby kompletne inteligentne lustro.

Zalecana:

Wyświetlacz matrycowy 8x8 z BT: 5 kroków (ze zdjęciami)

Wyświetlacz matrycowy 8x8 z BT: Kupiłem 4-panelową matrycę 8x8 z Ebay (Chiny) kilka miesięcy temu. Byłem trochę rozczarowany, gdy zdałem sobie sprawę, że jest to sztywno okablowana z boku na bok, a nie od góry do dołu, dla której większość przykładów na sieci są napisane! Zobacz krok 2. Myślę, że mógłbym mieć mo

Zrób zegar lustrzany Infinity: 15 kroków (ze zdjęciami)

Zrób zegar lustrzany nieskończoności: W poprzednim projekcie zbudowałem lustro nieskończoności, gdzie moim ostatecznym celem było przekształcenie go w zegar. (Zrób kolorowe lustro nieskończoności) Nie dążyłem do tego po zbudowaniu go, ponieważ chociaż wyglądało fajnie, było kilka rzeczy z

Wyświetlacz TTGO (kolorowy) z Micropythonem (wyświetlacz TTGO T): 6 kroków

Wyświetlacz TTGO (kolorowy) Z Micropythonem (wyświetlacz TTGO T): Wyświetlacz TTGO T to płyta oparta na ESP32, która zawiera 1,14-calowy kolorowy wyświetlacz. Deskę można kupić za cenę mniejszą niż 7$ (wliczając wysyłkę, nagrodę widzianą na banggood). To niesamowita nagroda za ESP32 z wyświetlaczem.T

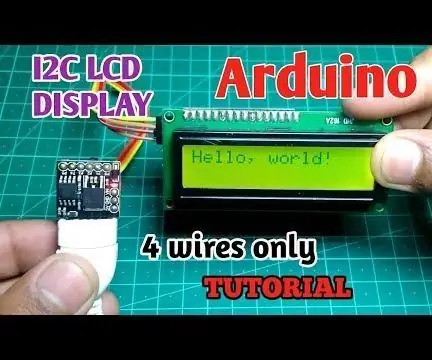

Wyświetlacz LCD I2C / IIC - Konwertuj wyświetlacz LCD SPI na wyświetlacz LCD I2C: 5 kroków

Wyświetlacz LCD I2C / IIC | Konwertuj wyświetlacz LCD SPI na wyświetlacz LCD I2C: używanie wyświetlacza LCD spi wymaga zbyt wielu połączeń, co jest naprawdę trudne, więc znalazłem moduł, który może przekonwertować wyświetlacz LCD i2c na wyświetlacz LCD spi, więc zaczynamy

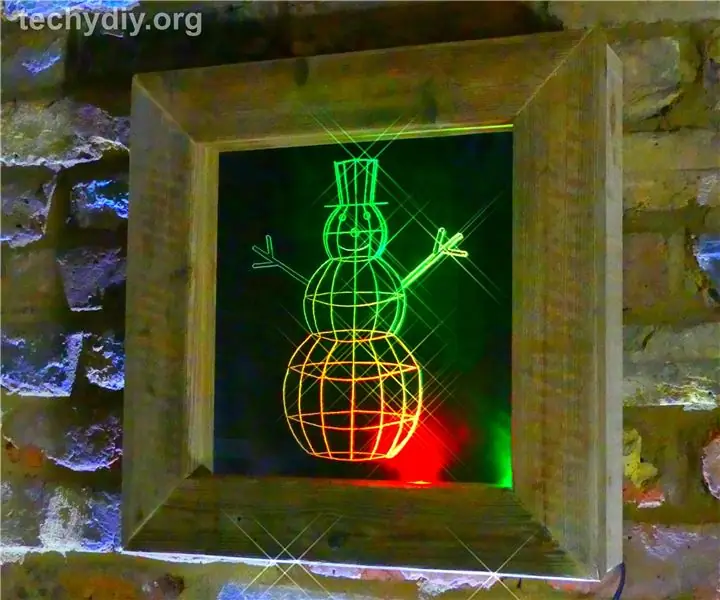

Znak lustrzany Snowman Led Edge Lit: 21 kroków (ze zdjęciami)

Snowman Led Edge Lit Mirror Sign: W tej instrukcji opiszę, jak można zrobić szklane lustro z podświetleniem led z motywem bałwana, idealne na Boże Narodzenie! Znak jest wygrawerowany na szklanej płytce lustrzanej z Ikei. Są one dostarczane w opakowaniach po cztery i są dość opłacalne. I