Spisu treści:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:31.

- Ostatnio zmodyfikowany 2025-06-01 06:10.

Buduję bramki tranzystorowe nieco inaczej niż większość innych inżynierów elektroników. Większość ludzi buduje bramki tranzystorowe; buduj je z myślą wyłącznie o logice pozytywnej, jednak bramki w układach scalonych mają dwie logiki, logikę pozytywną i logikę negatywną. I buduję swoje bramki tranzystorowe z logiką pozytywną i negatywną.

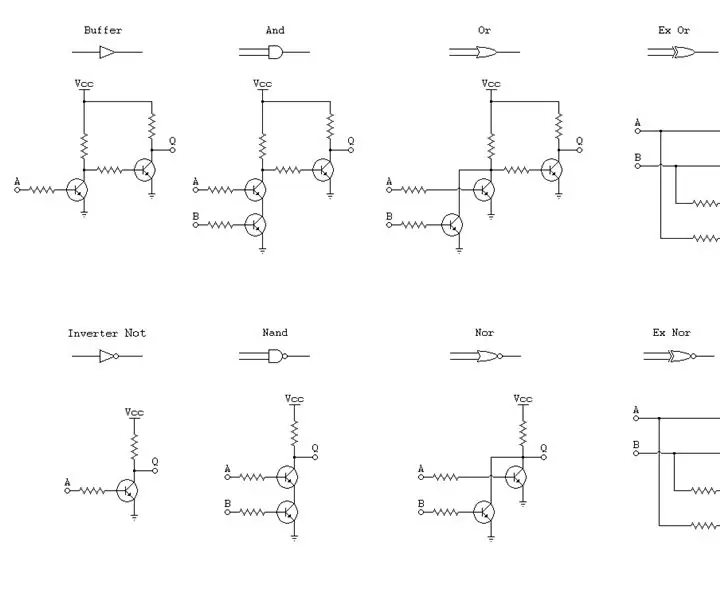

Chociaż istnieje osiem bram; Buffer, Inverter or Not, And, Nand, Or, Nor, Xor i Xnor, składają się z trzech obwodów bramki. A kiedy budujesz podwójne bramki logiczne, trzy obwody używane do budowy bramki to Inverter lub Not, Nand i Nor, reszta bramek jest wykonana z dwóch lub więcej z tych trzech bramek.

Po co budować bramki tranzystorowe? Oto pięć powodów, dla których warto zbudować własne bramy.

1. Nie masz bramy, której potrzebujesz.

2. Potrzebujesz bramki, która przenosi większą moc niż standardowa bramka IC.

3. Chcesz tylko jednej bramki i nienawidzisz marnować pozostałych bramek na IC.

4. Koszt, jeden tranzystorowy falownik kosztuje mniej niż 0,25 USD, a sześciokątny układ scalony falownika to 1,00 USD i więcej.

5. Chcesz lepiej zrozumieć bramy.

Krok 1: Narzędzia i części

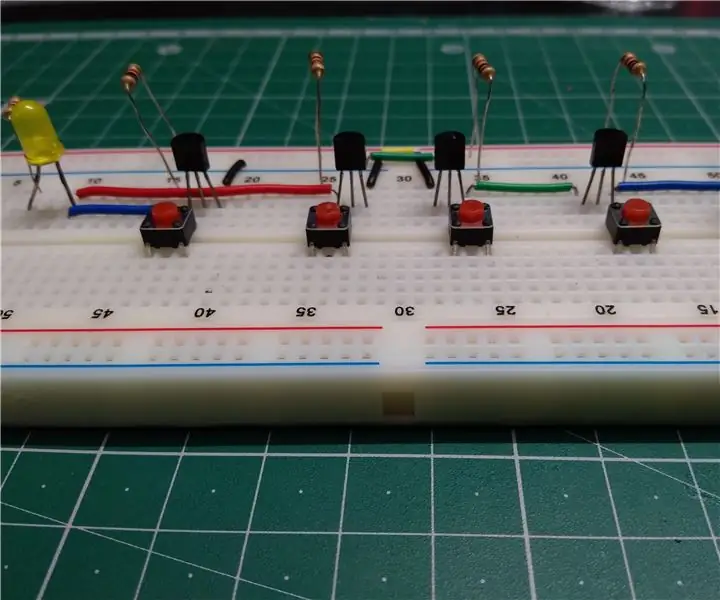

Bramki w tym Instructable są bramkami ¼ watowymi, jeśli chcesz budować bramy o wyższej mocy, będziesz potrzebować cięższych komponentów o mocy.

Przewody połączeniowe

Deska do krojenia chleba

Zasilacz

1 x układ scalony SN74LS04

2 x przełączniki

2 x diody LED 1 czerwona 1 zielona

Rezystory 2 x 820 Ω ¼ w

Rezystory 2 x 1 kΩ ¼ w

Rezystory 3 x 10 kΩ ¼ w

3 x tranzystory NPN ogólnego przeznaczenia, użyłem 2N3904.

Tranzystory ogólnego przeznaczenia 2 x PNP, użyłem 2N3906.

Krok 2: Podwójna logika

Kiedy spojrzysz w górę tabeli prawdy przy bramie; takich jak dwuwejściowa bramka lub bramka, otrzymasz tabelę prawdy, która wygląda tak. To jest pozytywna tabela prawdy dla bramki Or. Pod A i B znajdują się wejścia do bramki, a Q to wyjście. 1 reprezentuje wartość logiczną 1 lub + 5 woltów, a 0 reprezentuje wartość logiczną 0 lub 0 woltów. Więc kiedy większość ludzi buduje bramkę z tranzystorów, buduje ją na wartość logiczną 1 lub + 5 woltów i wartość logiczną 0 lub brak woltów. Ale to nie dzieje się z wyjściem bramki w układzie scalonym.

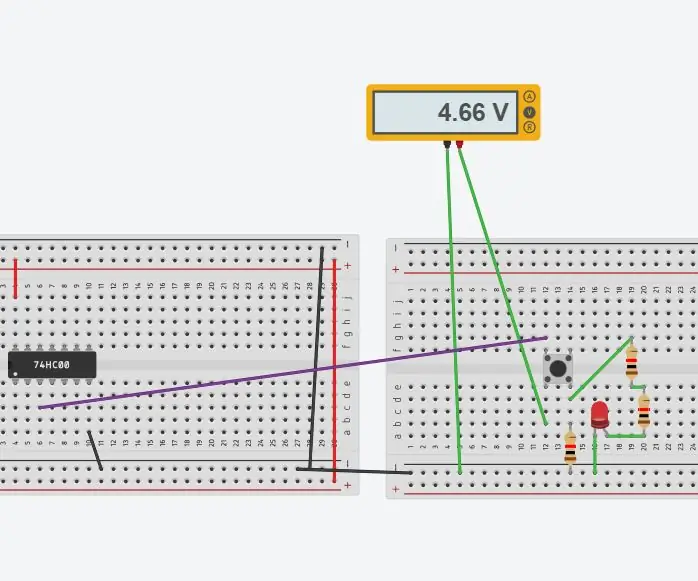

Gdy wyjście bramki przechodzi z wartości logicznej 1 do wartości logicznej 0, wyjście tej bramki przechodzi z + 5 woltów przy prądzie wypływającym z wyjścia do 0 woltów przy prądzie płynącym do wyjścia bramki. Prąd odwraca kierunek. Kiedy używasz odwróconego przepływu prądu, nazywa się to logiką ujemną, gdzie 0 woltów to - 1 wartość logiczna, a + 5 woltów to - 0 wartości logicznej.

Najłatwiej zobaczyć, co to robi, gdy podłączysz wyjście dowolnej bramki; do bazy tranzystora NPN i tranzystora PNP, szeregowo z diodą LED. Podczas gdy wyjście bramki ma wartość logiczną 1 (5 V), tranzystor NPN jest zamknięty, a dioda LED połączona szeregowo z tranzystorem NPN świeci. Gdy wyjście bramki przechodzi z wartości logicznej 1 do wartości logicznej 0 (5 V do 0 V), prąd zmienia kierunek i tranzystor NPN otwiera się, gdy tranzystor PNP się zamyka. Spowoduje to wyłączenie diody LED połączonej szeregowo z tranzystorem NPN i zaświecenie diody LED połączonej szeregowo z tranzystorem PNP.

Moje bramki tranzystorowe mają tę samą podwójną logikę, co bramki w układach scalonych. Podczas gdy wyjście bramki ma wartość logiczną 1 (5 V), tranzystor NPN jest zamknięty, a dioda LED połączona szeregowo z tranzystorem NPN świeci. Gdy wyjście bramki przechodzi z wartości logicznej 1 do wartości logicznej 0 (5 V do 0 V), prąd zmienia kierunek i tranzystor NPN otwiera się, gdy tranzystor PNP się zamyka. Spowoduje to wyłączenie diody LED połączonej szeregowo z tranzystorem NPN i zaświecenie diody LED połączonej szeregowo z tranzystorem PNP.

Krok 3: Nie lub bramka inwertera

Bramka Not lub Inverter jest pierwszą z 3 bramek potrzebnych do wykonania pozostałych 5 bramek.

Gdy wejście (A) bramki inwertera ma wartość 0 lub 0 V, tranzystor NPN jest otwarty, a wyjście (Q) wynosi 1 lub +5 V, a z wyjścia (Q) wychodzi prąd dodatni.

Gdy wejście (A) bramki inwertera wynosi 1 lub +5 V, tranzystor NPN jest zamknięty, a wyjście (Q) wynosi 0 lub 0 V, a każdy dodatni prąd przechodzi przez tranzystor do masy.

Krok 4: Brama Nand

Brama Nand jest drugą z trzech bram potrzebnych do wykonania pozostałych 5 bram.

Gdy wejścia (A i B) bramki Nand mają wartość 0 lub 0 woltów, oba tranzystory NPN są otwarte, a wyjście (Q) wynosi 1 lub + 5 woltów, a jakikolwiek prąd dodatni wychodzi z wyjścia (Q).

Gdy wejście (A) bramki Nand wynosi 1 lub +5 V, tranzystor NPN na wejściu A jest zamknięty. A gdy wejście (B) bramki Nand ma wartość 0 lub 0 V, tranzystor NPN na wejściu B jest otwarty, a wyjście (Q) wynosi 1 lub + 5 V, a z wyjścia (Q) wychodzi prąd dodatni..

Gdy wejście (A) bramki Nand ma wartość 0 lub 0 V, tranzystor NPN na wejściu A jest otwarty. A gdy wejście (B) bramki Nand wynosi 1 lub +5 V, tranzystor NPN na wejściu B jest zamknięty, a wyjście (Q) wynosi 1 lub +5 V, a jakikolwiek prąd dodatni wychodzi z wyjścia (Q).

Gdy wejścia (A i B) bramki Nand mają wartość 1 lub +5 woltów, oba tranzystory NPN są zamknięte, a wyjście (Q) ma wartość 0 lub 0 woltów, a każdy dodatni prąd przechodzi przez tranzystory do masy.

Krok 5: Ani Brama

Brama Nor jest trzecią z trzech bram potrzebnych do wykonania pozostałych 5 bram.

Gdy wejścia (A i B) bramki Nor mają wartość 0 lub 0 woltów, oba tranzystory NPN są otwarte, a wyjście (Q) wynosi 1 lub + 5 woltów, a jakikolwiek prąd dodatni wychodzi z wyjścia (Q).

Gdy wejście (A) bramki Nor wynosi 1 lub +5 V, tranzystor NPN na wejściu A jest zamknięty. A gdy wejście (B) bramki Nor wynosi 0 lub 0 V, tranzystor NPN na wejściu B jest otwarty, a wyjście (Q) ma 0 lub 0 V, a każdy dodatni prąd przechodzi do masy przez tranzystor na wejściu A.

Gdy wejście (A) bramki Nor wynosi 0 lub 0 V, tranzystor NPN na wejściu A jest otwarty. A kiedy wejście (B) bramki Nor wynosi 1 lub +5 V, tranzystor NPN na wejściu B jest zamknięty, a wyjście (Q) ma 0 lub 0 V, a każdy dodatni prąd przechodzi do masy przez tranzystor na B Wejście.

Gdy wejścia (A i B) bramki Nor mają wartość 1 lub + 5 woltów, oba tranzystory NPN są zamknięte, a wyjście (Q) wynosi 0 lub 0 woltów, a każdy dodatni prąd przechodzi do uziemienia przez oba tranzystory.

Krok 6: Bufor

Bufor używa dwóch takich samych bramek; dwie bramki Not lub Inverter połączone szeregowo.

Gdy wejście (A) pierwszej bramki falownika wynosi 0 lub 0 V, tranzystor NPN jest otwarty, a wyjście ma 1 lub +5 V na wejściu drugiego falownika. Gdy wejście drugiej bramki falownika wynosi 1 lub +5 V, tranzystor NPN jest zamknięty, a wyjście (Q) ma wartość 0 lub 0 V, a każdy dodatni prąd przechodzi przez tranzystor do masy.

Gdy wejście (A) pierwszej bramki falownika wynosi 1 lub +5 V, tranzystor NPN jest zamknięty, a wyjście ma 0 lub 0 V na wejściu drugiego falownika. Gdy wejście drugiej bramki falownika wynosi 0 lub 0 V, tranzystor NPN jest otwarty, a wyjście (Q) wynosi 1 lub +5 V, a każdy dodatni prąd wychodzi na wyjście (Q).

Krok 7: I brama

Brama And to bramka Nand i bramka Not lub Inverter w szeregu.

Wejścia są takie same jak bramka Nand, jednak wyjście jest odwracane przez bramkę Not lub Inverter.

Gdy wejścia (A i B) bramki And mają wartość 0 lub 0 woltów, oba tranzystory NPN są otwarte, wyjście pierwszej bramki wynosi 1 lub + 5 woltów. Gdy wejście bramki falownika wynosi 1 lub +5 V, tranzystor NPN jest zamknięty, a wyjście (Q) ma wartość 0 lub 0 V, a każdy dodatni prąd przechodzi przez tranzystor do masy.

Gdy wejście (A) bramki And wynosi 1 lub +5 V, tranzystor NPN na wejściu A jest zamknięty. A gdy wejście (B) bramki And ma wartość 0 lub 0 woltów, tranzystor NPN na wejściu B jest otwarty, wyjście pierwszej bramki wynosi 1 lub + 5 woltów. Gdy wejście bramki falownika wynosi 1 lub +5 V, tranzystor NPN jest zamknięty, a wyjście (Q) ma wartość 0 lub 0 V, a każdy dodatni prąd przechodzi przez tranzystor do masy.

Gdy wejście (A) bramki And ma wartość 0 lub 0 V, tranzystor NPN na wejściu A jest otwarty. A gdy wejście (B) bramki And wynosi 1 lub +5 woltów, tranzystor NPN na wejściu B jest zamknięty, wyjście pierwszej bramki wynosi 1 lub +5 woltów. Gdy wejście bramki falownika wynosi 1 lub +5 V, tranzystor NPN jest zamknięty, a wyjście (Q) ma wartość 0 lub 0 V, a każdy dodatni prąd przechodzi przez tranzystor do masy.

Gdy wejścia (A i B) bramki Nand mają wartość 1 lub +5 woltów, oba tranzystory NPN są zamknięte, a wyjście pierwszej bramki ma wartość 0 lub 0 woltów. Gdy wejście bramki falownika ma wartość 0 lub 0 V, tranzystor NPN jest otwarty, a wyjście (Q) ma wartość 1 lub +5 V, a jakikolwiek prąd dodatni wychodzi na wyjście (Q).

Krok 8: Lub brama

Bramka Or jest bramką Nor i bramką Not lub Inverter w szeregu.

Wejścia są takie same jak bramka Nor, jednak wyjście jest odwracane przez bramkę Not lub Inverter.

Gdy wejścia (A i B) bramki Or mają wartość 0 lub 0 woltów, oba tranzystory NPN są otwarte, wyjście pierwszej bramki wynosi 1 lub +5 woltów. Gdy wejście bramki falownika wynosi 1 lub +5 V, tranzystor NPN jest zamknięty, a wyjście (Q) ma wartość 0 lub 0 V, a każdy dodatni prąd przechodzi przez tranzystor do masy.

Gdy wejście (A) bramki Or wynosi 1 lub +5 V, tranzystor NPN na wejściu A jest zamknięty. A gdy wejście (B) bramki Nor ma wartość 0 lub 0 woltów, tranzystor NPN na wejściu B jest otwarty, a wyjście pierwszej bramki ma wartość 0 lub 0 woltów. Gdy wejście bramki falownika ma wartość 0 lub 0 V, tranzystor NPN jest otwarty, a wyjście (Q) ma wartość 1 lub +5 V, a jakikolwiek prąd dodatni wychodzi na wyjście (Q).

Gdy wejście (A) bramki Or ma wartość 0 lub 0 V, tranzystor NPN na wejściu A jest otwarty. A gdy wejście (B) bramki Nor wynosi 1 lub +5 woltów, tranzystor NPN na wejściu B jest zamknięty, a wyjście pierwszej bramki ma wartość 0 lub 0 woltów. Gdy wejście bramki falownika ma wartość 0 lub 0 V, tranzystor NPN jest otwarty, a wyjście (Q) ma wartość 1 lub +5 V, a jakikolwiek prąd dodatni wychodzi na wyjście (Q).

Gdy wejścia (A i B) bramki Or mają wartość 1 lub +5 woltów, oba tranzystory NPN są zamknięte, a wyjście pierwszej bramki ma wartość 0 lub 0 woltów. Gdy wejście bramki falownika ma wartość 0 lub 0 V, tranzystor NPN jest otwarty, a wyjście (Q) ma wartość 1 lub +5 V, a jakikolwiek prąd dodatni wychodzi na wyjście (Q).

Krok 9: Ekskluzywna Brama Nor (Xnor)

Ekskluzywna bramka Nor jest skonfigurowana jako dwie bramki Nand połączone równolegle jako bramka Nor z dwoma górnymi tranzystorami PNP.

Gdy wejścia (A i B) bramki Xnor mają wartość 0 lub 0 woltów, oba tranzystory NPN są otwarte, a oba tranzystory PNP są zamknięte. Wyjście (Q) wynosi 1 lub +5 woltów, a każdy dodatni prąd wychodzi z wyjścia (Q).

Gdy wejście (A) bramki Xnor wynosi 1 lub +5 V, tranzystor NPN na wejściu A jest zamknięty, a tranzystor PNP jest otwarty. Gdy wejście (B) bramki Xnor wynosi 0 lub 0 V, tranzystor PNP na wejściu B jest zamknięty, a tranzystor NPN jest otwarty. Wyjście (Q) wynosi 0 lub 0 woltów, a każdy dodatni prąd trafia do masy przez zamknięte tranzystory.

Gdy wejście (A) bramki Xnor ma wartość 0 lub 0 V, tranzystor NPN na wejściu A jest otwarty, a tranzystor PNP jest zamknięty. Gdy wejście (B) bramki Xnor wynosi 1 lub +5 V, tranzystor PNP na wejściu B jest otwarty, a tranzystor NPN jest zamknięty. Wyjście (Q) wynosi 0 lub 0 woltów, a każdy dodatni prąd trafia do masy przez zamknięte tranzystory.

Gdy wejścia (A i B) bramki Xnor mają wartość 1 lub +5 V, oba tranzystory NPN są zamknięte, a oba tranzystory PNP są otwarte. Wyjście (Q) wynosi 1 lub +5 woltów, a każdy dodatni prąd wychodzi z wyjścia (Q).

Krok 10: Ekskluzywny lub Brama (Xor)

Brama Exclusive Or; wykorzystuje wszystkie trzy kluczowe bramki, jest skonfigurowany jako dwie bramki Nand połączone równolegle jako bramka Nor z dwoma górnymi tranzystorami tranzystorami PNP i bramką Not lub Inverter szeregowo.

Wejścia bramki Xor są takie same jak bramka Xnor, jednak wyjście jest odwracane przez bramkę Not lub Inverter.

Gdy wejścia (A i B) bramki Xnor mają wartość 0 lub 0 woltów, oba tranzystory NPN są otwarte i oba tranzystory PNP są zamknięte, a wyjście pierwszego zestawu bramek ma wartość 1 lub +5 woltów. Gdy wejście bramki falownika wynosi 1 lub +5 V, tranzystor NPN jest zamknięty, a wyjście (Q) ma wartość 0 lub 0 V, a każdy dodatni prąd przechodzi przez tranzystor do masy.

Gdy wejście (A) bramki Xnor wynosi 1 lub +5 V, tranzystor NPN na wejściu A jest zamknięty, a tranzystor PNP jest otwarty. Gdy wejście (B) bramki Xnor wynosi 0 lub 0 woltów, tranzystor PNP na wejściu B jest zamknięty, a tranzystor NPN jest otwarty, 0 lub 0 woltów na wejściu falownika. Gdy wejście bramki falownika ma wartość 0 lub 0 V, tranzystor NPN jest otwarty, a wyjście (Q) ma wartość 1 lub +5 V, a jakikolwiek prąd dodatni wychodzi na wyjście (Q).

Gdy wejście (A) bramki Xnor ma wartość 0 lub 0 V, tranzystor NPN na wejściu A jest otwarty, a tranzystor PNP jest zamknięty. Gdy wejście (B) bramki Xnor wynosi 1 lub +5 V, tranzystor PNP na wejściu B jest otwarty, a tranzystor NPN jest zamknięty, 0 lub 0 V na wejściu falownika. Gdy wejście bramki falownika ma wartość 0 lub 0 V, tranzystor NPN jest otwarty, a wyjście (Q) ma wartość 1 lub +5 V, a jakikolwiek prąd dodatni wychodzi na wyjście (Q).

Gdy wejścia (A i B) bramki Xnor mają wartość 1 lub +5 V, oba tranzystory NPN są zamknięte, a oba tranzystory PNP są otwarte. Gdy napięcie na wejściu drugiej bramki falownika wynosi 1 lub +5 V, tranzystor NPN tranzystor jest zamknięty, a wyjście (Q) ma wartość 0 lub 0 woltów, a każdy dodatni prąd przechodzi przez tranzystor do masy.

Drugie miejsce w wyzwaniu „Porady i wskazówki dotyczące elektroniki”

Zalecana:

Bramki logiczne wykorzystujące tranzystor: 3 kroki

Bramki logiczne wykorzystujące tranzystor: Bramki logiczne są podstawowymi elementami składowymi każdego systemu cyfrowego

Wykorzystanie obwodu do pomiaru napięcia bramki cyfrowej: 7 kroków

Korzystanie z obwodu do pomiaru napięcia bramki cyfrowej: Obwody cyfrowe zwykle wykorzystują zasilacze 5 V. Napięcia cyfrowe od 5 V do 2,7 V w serii TTL (rodzaj cyfrowego zintegrowanego układu scalonego) są uważane za wysokie i mają wartość 1. Napięcia cyfrowe formularz 0-0,5 są uważane za niskie i mają

Szybkie i brudne konwertery tranzystorowe SMD SOT: 4 kroki

Szybkie i brudne konwertery tranzystorowe SMD SOT: Czasami trzeba podłączyć przewody do tranzystora do montażu powierzchniowego. Niektóre powody, dla których możesz chcieć to zrobić, to: masz odzyskany tranzystor, którego chcesz użyć, który akurat jest montowany powierzchniowo, chcesz wypróbować coś na bezlutowanej chlebaku

Jak naprawić podwójne kliknięcie myszą: 5 kroków

Jak naprawić podwójne kliknięcie myszy: Podwójne kliknięcie spowodowane sprężyną w przełączniku myszy. Sprężyna ta może się zmęczyć, więc nie zapewnia nacisku niezbędnego do utrzymania połączenia między dwoma stykami (góra, dół). Dzięki połączeniu brudu, ścierania i utleniania na obszarach styku, ja

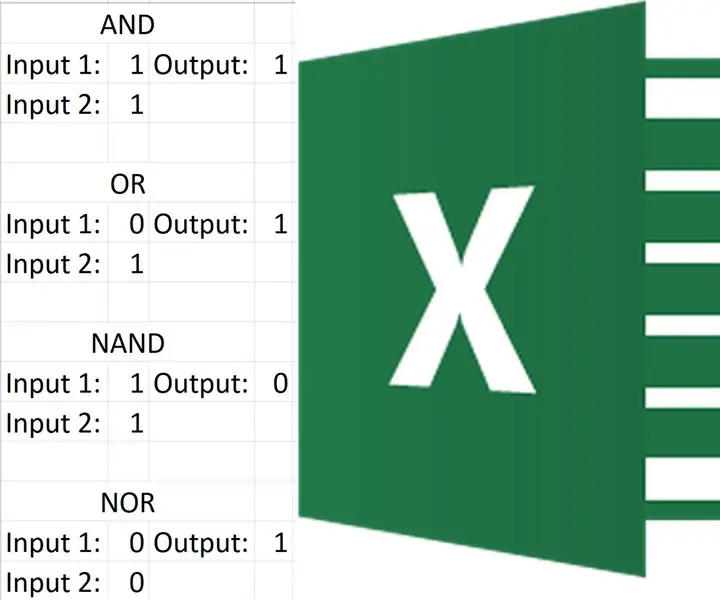

Utwórz bramki logiczne w Excelu: 11 kroków

Utwórz bramki logiczne w programie Excel: Tworzenie wszystkich 7 podstawowych bramek logicznych w programie Excel nie jest trudne. Jeśli rozumiesz funkcje w Excelu, ten projekt byłby dość prosty, jeśli nie, nie martw się, przyzwyczajenie się do niego nie potrwa długo. Excel już stworzył kilka bramek logicznych dla