Spisu treści:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:28.

- Ostatnio zmodyfikowany 2025-01-23 15:02.

By AmCoderhttps://www.linkedin.com/in/mituFollow Więcej autora:

O: Mitu Raj -- Po prostu hobbysta i uczeń -- Projektant chipów -- Programista -- Entuzjasta fizyki i matematyki Więcej o AmCoder »

##Jest to najczęściej klikany, popularny link w Google do implementacji algorytmu CORDIC ALGORYTM w języku VHDL do generowania fali sinusoidalnej i kosinusoidalnej## Obecnie istnieje wiele wydajnych algorytmów sprzętowych, ale nie są one dobrze znane ze względu na dominację systemów oprogramowania wiele lat. Takim algorytmem jest CORDIC, który jest niczym innym jak zbiorem logik przesunięcia i dodawania służących do obliczania szerokiego zakresu funkcji, w tym pewnych funkcji trygonometrycznych, hiperbolicznych, liniowych i logarytmicznych. Jest to algorytm używany w kalkulatorach itp. Tak więc używając prostych przełączników i sumatorów możemy zaprojektować sprzęt o mniejszej złożoności, ale o mocy DSP przy użyciu algorytmu cordic. Dlatego może być zaprojektowany jako czysty projekt RTL w VHDL lub Verilog bez użycia dedykowanych jednostek zmiennoprzecinkowych lub złożonych matematycznych adresów IP.

Krok 1: VHDL i Modelsim

Tutaj algorytm kordowy jest zaimplementowany przy użyciu VHDL do generowania fali sinusoidalnej i fali cose. Może z dużą precyzją wyprowadzać sinus i cosinus kąta wejściowego. Kod można zsyntetyzować na FPGA. Modelsim służy do symulacji projektu i stanowiska testowego.

Krok 2: Kod VHDL do projektowania i stanowiska testowego

Technika skalowania binarnego służy do reprezentowania liczb zmiennoprzecinkowych.

Przed przystąpieniem do kodowania zapoznaj się z załączonymi dokumentami.

Przejdź przezSimulating cordic_v4.vhd - Projekt - Dane wejściowe to kąt w 32 bitach + bit znaku; może przetwarzać dowolny kąt od 0 do +/-360 stopni z dokładnością wejściową 0,0000000000233 stopni. Podając dane wejściowe -> MSB to bit znaku, a pozostałe 32 bity reprezentują wielkość.-Wyjście projektu to jego wartość sinus i cos w 16 bitach + bit znaku.ie; z dokładnością 0.00001526. Należy pamiętać, że wynik jest wyświetlany w formie komplementu 2, jeśli odpowiednia wartość sinusa lub cos jest ujemna. Symulacja testb.vhd - Stanowisko testowe do projektowania (1) Wprowadź kąty i zresetuj ciąg ='0'. Po dwóch krokach symulacji przeciągnij zresetuj do '1' i "uruchom wszystko". (2) W oknie symulacji ustaw podstawę sygnałów sin i cos jako dziesiętną i format > Analog (automatycznie). (3) Oddal, aby zobaczyć przebieg odpowiednio.

Krok 3: Załączone pliki

(1) cordic_v4.vhd - Projekt.(2) testb.vhd - Stanowisko badawcze do projektowania.

(3) Dokument, w jaki sposób wymuszać wprowadzanie kątów i konwertować wyniki binarne.

Aktualizacja: TE PLIKI SĄ PRZESTARZAŁE I NIE JEST JUŻ DOSTARCZANE. PROSZĘ UŻYWAĆ PLIKÓW Z NASTĘPNEGO KROKU

Krok 4: Mini-Cordic IP Core - 16 bitów

Ograniczeniem powyższej implementacji jest powolna, niższa częstotliwość taktowania pracy z powodu wykonywania obliczeń w jednym cyklu zegara. Mini-Cordic IP Core - 16 Bit

- Ścieżki krytyczne dystrybuowane do wielu cykli w celu poprawy wydajności. - Szybsze - Sprawdzona konstrukcja FPGA zsyntetyzowana do zegara do 100 Mhz. - Większy obszar zoptymalizowany w HDL, mniejszy sprzęt. - Dodano sygnały stanu obciążenia i wykonania. - Jedynym minusem jest mniejsza rozdzielczość w porównaniu do poprzedni. Testbench:

całkowicie zautomatyzowany od 0 do 360 stopni kąta wejścia

Załączone pliki:1) główny plik vhdl mini cordic2) stół testowy mini cordic3) instrukcja obsługi Mini Cordic IP Core4) Dokument na temat wymuszania kątów i konwertowania wyników

W przypadku jakichkolwiek pytań zapraszam do kontaktu:

Mitu Raj

śledź mnie:

mail: iammituraj@gmail.com

###Łączna liczba pobrań: 325 do 01-05-2021###

### Ostatnia edycja kodu: 07.07.2020 ###

Zalecana:

Pierwsze kroki z Digispark Attiny85 przy użyciu Arduino IDE: 4 kroki

Rozpoczęcie pracy z Digispark Attiny85 przy użyciu Arduino IDE: Digispark to oparta na Attiny85 płytka rozwojowa mikrokontrolera podobna do linii Arduino, tylko tańsza, mniejsza i nieco mniej wydajna. Z całą gamą osłon rozszerzających jego funkcjonalność i możliwością korzystania ze znanego identyfikatora Arduino

Neopixel Ws2812 Rainbow LED Glow z M5stick-C - Uruchamianie Rainbow na Neopixel Ws2812 przy użyciu M5stack M5stick C przy użyciu Arduino IDE: 5 kroków

Neopixel Ws2812 Rainbow LED Glow z M5stick-C | Uruchamianie Rainbow na Neopixel Ws2812 Używając M5stack M5stick C Używając Arduino IDE: Cześć chłopaki, w tej instrukcji dowiemy się, jak używać neopikselowych ws2812 LED lub taśmy LED lub matrycy LED lub pierścienia LED z płytką rozwojową m5stack m5stick-C z Arduino IDE i zrobimy wzór tęczy z nim

Pierwsze kroki z Stm32 przy użyciu Arduino IDE: 3 kroki

Pierwsze kroki z Stm32 przy użyciu Arduino IDE: STM32 to dość potężna i popularna płyta obsługiwana przez Arduino IDE. Aby z niej skorzystać, musisz zainstalować płyty dla stm32 w Arduino IDE, więc w tej instrukcji opowiem, jak zainstalować płyty stm32 i jak zaprogramować to

Przetwarzanie wideo przy użyciu VHDL i Zybo: 10 kroków

Przetwarzanie wideo przy użyciu VHDL i Zybo: FPGA są szybsze niż procesory w przetwarzaniu, ponieważ mogą wykonywać wiele obliczeń równolegle Uwaga: Ten projekt jest wciąż w budowie i będzie ulepszany (jak tylko będę miał czas). W międzyczasie podróżuję po świecie

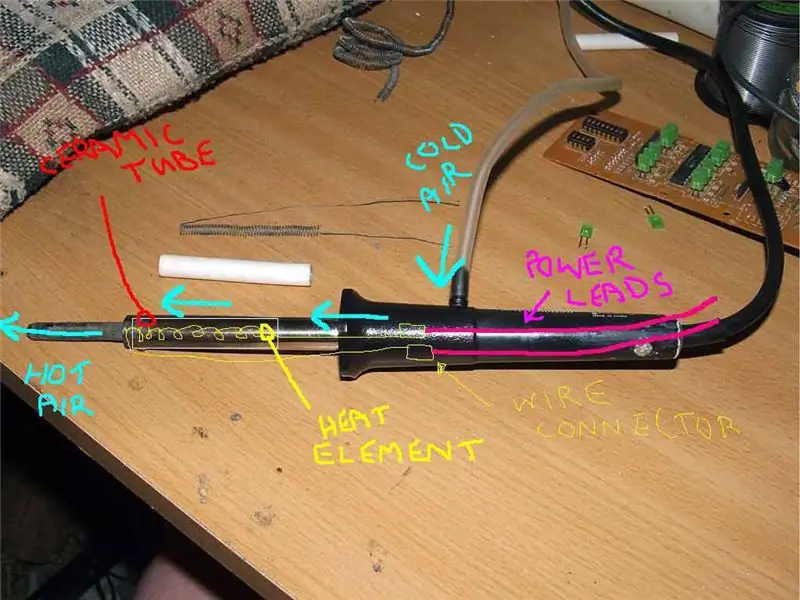

DIY lutownica na gorące powietrze przy użyciu 12-18 woltów prądu stałego przy 2-3 amperach: 18 kroków (ze zdjęciami)

DIY lutownica na gorące powietrze przy użyciu 12-18 woltów prądu stałego przy 2-3 amperach: to moja pierwsza publikacja eva artykułu o majsterkowaniu w Internecie. Więc przepraszam za literówki, protokoły itp. Poniższe instrukcje pokazują, jak zrobić PRACOWĄ lutownicę na gorące powietrze odpowiednią do WSZYSTKICH zastosowań wymagających lutowania. To lutowanie gorącym powietrzem