Spisu treści:

- Krok 1: Schemat blokowy

- Krok 2: Zasada działania

- Krok 3: Implementacja logiki

- Krok 4: Rozwiązanie problemu impasu

- Krok 5: Konfiguracja urządzenia - obwód Matrix0

- Krok 6: Konfiguracja urządzenia - logika taktowania SPI

- Krok 7: Konfiguracja urządzenia - właściwości składników Matrix0

- Krok 8: Konfiguracja urządzenia - obwód Matrix1

- Krok 9: Konfiguracja urządzenia - 3-bitowy licznik binarny

- Krok 10: Konfiguracja urządzenia - 3-bitowa logika porównania

- Krok 11: Konfiguracja urządzenia - cyfrowe porównywanie logiki i rejestru tymczasowego

- Krok 12: Konfiguracja urządzenia - Właściwości składników macierzy 1

- Krok 13: Wyniki

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:28.

- Ostatnio zmodyfikowany 2025-01-23 15:02.

Systemy sterowania i powiązane urządzenia obsługują wiele źródeł zasilania, takich jak linie polaryzacji lub baterie, i muszą śledzić najwyższą (lub najniższą) linię w danym zestawie.

Na przykład przełączanie obciążenia w systemie zasilanym „wieloma bateriami” wymaga, aby system monitorował minimalne lub maksymalne napięcie w tablicy akumulatorów (maksymalne lub minimalne jako funkcja danego algorytmu przełączania) i dynamicznie kierował obciążenie do najbardziej odpowiednie źródło w czasie rzeczywistym. Alternatywnie system może wymagać tymczasowego odłączenia akumulatora o najniższym napięciu w celu prawidłowego ładowania.

Innym przykładem jest nowoczesny system zasilania energią słoneczną, w którym każdy panel słoneczny jest wyposażony w mechanizm odchylania i obwód śledzenia słońca (ten ostatni dostarcza informacje o położeniu Słońca w celu orientacji panelu). Dzięki informacjom o maksymalnym napięciu każda pozycja panelu słonecznego może być dostrojona na podstawie tego, czy panel ciągu faktycznie dostarcza najwyższe napięcie wyjściowe, osiągając w ten sposób najwyższy poziom optymalizacji mocy.

Istnieje kilka różnych marek komercyjnych układów scalonych (głównie mikrokontrolerów), które w zasadzie mogą implementować wtórnik maksymalnego napięcia. Wymagają jednak programowania i są mniej opłacalne niż rozwiązanie z mieszanym sygnałem. Uzupełnienie projektu Dialog GreenPAKTM może pozytywnie wpłynąć na przystępność, rozmiar i modułowość projektu. Ten projekt wykorzystuje zalety integracji obwodów analogowych i cyfrowych w jednym układzie scalonym.

W tym Instruktażowym zaimplementowano analogowy front-end i cyfrową logikę wymagane do zaimplementowania maksymalnego (lub ostatecznie minimalnego) szukacza napięcia wśród ośmiu różnych źródeł.

Do realizacji 8-kanałowego analogowego monitora napięcia max/min zastosowano SLG46620G.

Poniżej opisaliśmy kroki potrzebne do zrozumienia, w jaki sposób zostało zaprogramowane rozwiązanie, aby stworzyć 8-kanałowy analogowy monitor napięcia max/min. Jeśli jednak chcesz tylko uzyskać wynik programowania, pobierz oprogramowanie GreenPAK, aby wyświetlić już ukończony plik projektu GreenPAK. Podłącz GreenPAK Development Kit do komputera i uruchom program, aby stworzyć 8-kanałowy analogowy monitor napięcia max/min.

Krok 1: Schemat blokowy

Rysunek 1 przedstawia globalny schemat wdrożonego systemu.

Ciąg do 8 źródeł o zmiennym napięciu jest multipleksowany i połączony z modułem ADC GreenPAK podłączonym do niestandardowej konstrukcji wewnętrznej zdolnej do wyboru źródła o najwyższym napięciu w stosunku do innych. Wewnętrzna logika wyprowadza te informacje do wyświetlenia lub dalszego przetwarzania.

Konstrukcja oparta jest na produkcie GreenPAK SLG46620G, ponieważ zawiera wszystkie niezbędne analogowe i cyfrowe bloki konstrukcyjne dla aplikacji. W tej implementacji macierz jest skanowana za pomocą analogowego multipleksera ADG508 sterowanego bezpośrednio przez układ GreenPAK IC.

Informacja wyjściowa to 3-bitowa liczba cyfrowa odpowiadająca numerowi źródła napięcia przy maksymalnym napięciu. Bezpośrednim sposobem uzyskania tych informacji jest pokazanie numeru za pomocą 7-segmentowego wyświetlacza. Można to łatwo osiągnąć, łącząc wyjście cyfrowe SLG46620G z 7-segmentowym sterownikiem wyświetlacza, takim jak rozwiązanie GreenPAK opisane w Reference lub ze zwykłym układem scalonym 74LS47.

Prezentowany układ szuka maksymalnego napięcia. Aby przekształcić projekt w wykrywacz minimalnego napięcia, należy dodać prosty obwód wstępnego kondycjonowania między multiplekserem analogowym a wejściem analogowym GreenPAK, odejmując sygnał wyjściowy multipleksera od napięcia odniesienia 1 V.

Krok 2: Zasada działania

Projekt ma na celu wybór źródła o maksymalnym napięciu, dlatego skanowanie jest wykonywane na całej tablicy, jednocześnie zapamiętując ostatnią wartość maksymalną i porównując ją z następną wartością na wejściu (która należy do następnego źródła napięcia w skanie).

Poniżej pełna sekwencja multipleksowania na wszystkich wejściach będzie nazywana „skanowaniem” lub „pętlą”.

Porównanie dwóch wartości nie jest realizowane za pomocą komponentów ACMP (jednak dostępne w SLG46620G), ale raczej przez moduł DCMP, gdy wartości zostaną odpowiednio zdigitalizowane. Jest to zaawansowana i wyrafinowana technika po raz pierwszy omówiona w Reference.

Rysunek 2 przedstawia strukturę SLG46620G dla tego projektu.

Analogowy sygnał wejściowy trafia do wejścia ADC przez komponent PGA z ustawionym wzmocnieniem na 1. Możliwe są również różne ustawienia wzmocnienia, aby znaleźć najlepsze dopasowanie z elektroniką kondycjonującą front-end, poświęconą mapowaniu napięć wejściowych do 0-1 V zakres modułu GreenPAK ADC.

ADC działa w trybie single-ended i konwertuje sygnał analogowy na 8-bitowy kod cyfrowy, który jest następnie przesyłany do modułu DCMP. Kod cyfrowy jest również wprowadzany do bloku SPI, skonfigurowanego jako bufor ADC/FSM, w którym kod cyfrowy może być przechowywany i nie zmienia się do momentu pojawienia się następnego impulsu na wejściu SPI CLK. Zauważ, że dedykowany blok logiczny steruje wejściem SPI CLK. Tę część zajmiemy się później, ponieważ jest to „podstawowa” logika odpowiedzialna za prawidłowe działanie. Nowy kod cyfrowy jest przechowywany w module SPI tylko wtedy, gdy należy do rzeczywistego maksymalnego napięcia wejściowego.

Składnik DCMP służy do porównywania bieżących danych ADC z ostatnim zwycięzcą (czyli ostatnim znalezionym maksimum), który jest przechowywany w bloku SPI. Wygeneruje impuls na wyjściu OUT+, gdy nowe dane ADC będą większe niż poprzednie. Używamy sygnału OUT+, aby zaktualizować blok SPI o nowego zwycięzcę.

Globalny sygnał zegarowy steruje konwersją ADC i ogólnymi czasami. Po wykonaniu konwersji impulsy sygnału wyjściowego INT przetwornika ADC są skoordynowane w czasie z równoległym wyjściem danych ADC. Używamy wyjścia INT również do inkrementacji 3-bitowego licznika binarnego, zaimplementowanego przez DFF w Matrix1, co jest przydatne z trzech powodów:

1. Linie wyjściowe licznika adresują zewnętrzny multiplekser analogowy, obsługując w ten sposób następne napięcie wejściowe do ADC;

2. Licznik jest zamrożony w 3-bitowym rejestrze (zaimplementowanym w Matrix1), aby zapisać tymczasowego zwycięzcę podczas skanowania;

3. Licznik jest dekodowany w celu aktualizacji drugiego rejestru 3-bitowego (zaimplementowanego w Matrix0) po zakończeniu skanowania.

Krok 3: Implementacja logiki

Moduł ADC sekwencyjnie dostarcza przekonwertowane dane wszystkich napięć wejściowych, jedno po drugim, w nieskończoność. Gdy multiplekser zostanie zaadresowany 0b111 (dziesiętnie 7), licznik zlicza się do 0b000 (dziesiętnie 0), rozpoczynając w ten sposób nowy skan napięć wejściowych.

Podczas skanowania sygnał wyjściowy ADC INT jest generowany, gdy równoległe wyjście danych jest prawidłowe. Kiedy ten sygnał pulsuje, multiplekser analogowy musi przełączyć się na następne wejście, dostarczając do PGA odpowiednie napięcie. Dlatego wyjście ADC INT jest bezpośrednim sygnałem taktowania 3-bitowego licznika binarnego z rysunku 2, którego 3-bitowe równoległe słowo wyjściowe bezpośrednio adresuje zewnętrzny multiplekser analogowy („V select” na rysunku 1).

Przyjrzyjmy się teraz przykładowi, w którym napięcia wejściowe mają mieć następujące zależności:

a) V0 < V1 < V2

b) V2 > V3, V4

c) V5 > V2

Rysunek 3 przedstawia główne sygnały zaangażowane w mechanizm maksymalnej decyzji.

Ponieważ dane są ostatecznie taktowane do rejestru bufora SPI synchronicznie z impulsami INT, istnieje okno porównania, w którym zawartość bufora SPI jest porównywana z następnym wynikiem konwersji ADC. To szczególne taktowanie powoduje generowanie impulsów OUT+ na wyjściu DCMP. Możemy wykorzystać te impulsy do załadowania nowych wartości do rejestru bufora SPI.

Jak widać z wiersza danych bufora SPI na poprzednim rysunku, rejestr SPI zawsze zawiera, w czasie, największą wartość spośród 8 wejść i jest aktualizowany tylko wtedy, gdy moduł DCMP wykryje większą wartość (odnosi się do DCMP OUT+ linii wyjściowej wykresu, brakujące impulsy powodują, że V2 pozostaje w rejestrze aż do porównania z V5).

Krok 4: Rozwiązanie problemu impasu

Jeśli zaimplementowana logika byłaby taka jak opisano powyżej, jasne jest, że wpadlibyśmy w sytuację impasu: system jest w stanie wykryć tylko napięcia wyższe niż to, które odpowiada temu, co jest zapisane w rejestrze buforowym SPI.

Jest to również ważne w przypadku, gdy napięcie to spadnie, a następnie inne wejście, dotychczas niższe niż to, stanie się najwyższe: nigdy nie zostanie wykryte. Ta sytuacja jest lepiej wyjaśniona na rysunku 4, gdzie obecne są tylko 3 napięcia wejściowe ze względu na przejrzystość.

W momencie iteracji 2 V3 spada, a V1 jest rzeczywistym maksymalnym napięciem. Ale moduł DCMP nie dostarcza impulsu, ponieważ dane przechowywane w rejestrze buforowym SPI (odpowiadające 0,6 V) są większe niż te odpowiadające V1 (0,4 V).

System zachowuje się wtedy jak „bezwzględny” wyszukiwacz maks. i nie aktualizuje poprawnie danych wyjściowych.

Dobrym sposobem na przezwyciężenie tego problemu jest wymuszenie ponownego załadowania danych do rejestru buforów SPI, gdy system zakończy pełny cykl odpytywania wszystkich kanałów.

W rzeczywistości, jeśli napięcie na tym wejściu jest nadal najwyższe, nic się nie zmienia i sterowanie jest bezpiecznie kontynuowane (patrz rysunek 4 powyżej, jest to przypadek iteracji pętli 0 i 1). Z drugiej strony, jeśli napięcie na tym wejściu przypadkowo obniży się do wartości mniejszej niż na innym wejściu, to ponowne załadowanie wartości daje modułowi DCMP możliwość wytworzenia impulsu OUT+ przy porównaniu go z nową wartością max (jest to przypadku iteracji pętli 2 i 3).

Aby rozwiązać problem, niezbędny jest kawałek obwodu logicznego. Musi generować sygnał zegarowy do komponentu SPI, gdy pętla osiągnie rzeczywisty maksymalny sygnał wejściowy, wymuszając w ten sposób ponowne załadowanie zaktualizowanego słowa danych do rejestru buforowego SPI. Zostanie to omówione w sekcjach 7.2 i 7.6 poniżej.

Krok 5: Konfiguracja urządzenia - obwód Matrix0

SLG46620G ma dwa bloki Matrix, jak pokazano na Rysunku 2. Poniższe rysunki przedstawiają odpowiednie konfiguracje urządzeń.

Górną częścią układu jest „Rejestr pętli” zrealizowany z 3 DFF (DFF0, DFF1 i DFF2). Jest odświeżany po każdej pętli multipleksera wejściowego, aby wysłać do 7-segmentowego sterownika wyświetlacza liczbę binarną „zwycięzcy”, czyli wejścia o najwyższym napięciu w ostatnim skanie. Zarówno zegar do DFF, jak i dane pochodzą z logiki zaimplementowanej w Matrix1 przez odpowiednio porty P12, P13, P14 i P15.

Dolna część to analogowy front end z wejściem na Pin 8 i PGA ze wzmocnieniem x1. Wyjście ADC INT trafia zarówno do logiki taktowania SPI, jak i do Matrix1 przez port P0, gdzie będzie służyć jako sygnał zegarowy dla zaimplementowanego licznika.

Równoległe wyjścia danych ADC i SPI są odpowiednio oznaczone jako NET11 i NET15, aby można je było podłączyć do komponentu DCMP w Matrix1.

Krok 6: Konfiguracja urządzenia - logika taktowania SPI

Jak wskazano wcześniej w sekcji „Implementacja logiki”, rejestr bufora SPI jest aktualizowany za każdym razem, gdy porównanie między rzeczywistą zapisaną wartością a nowymi danymi konwersji ADC generuje impuls na wyjściu DCMP OUT+.

Integralność sygnału jest zapewniona, jeśli ten sygnał jest połączony AND z wyjściem ADC INT. Pozwala to uniknąć skoków i fałszywego wyzwalania.

Podkreśliliśmy również, że aby uniknąć sytuacji impasu, bufor SPI musi zostać zaktualizowany, gdy pętla osiągnie rzeczywiste dane zwycięzcy.

W grze są więc trzy sygnały dla prawidłowego taktowania SPI:

1. Wyjście ADC INT (LUT0-IN1)

2. Wyjście DCMP OUT+ (LUT0-IN0 przez port P10)

3. Liczba równa się sygnałowi zatrzasku (LUT0-IN2 przez port P11)

Pierwsze dwa to AND i oba OR-ed z drugim w LUT0, którego implementacja jest skonfigurowana jak na rysunku 6.

Krok 7: Konfiguracja urządzenia - właściwości składników Matrix0

Rysunki 7-10 pokazują okna właściwości pozostałych komponentów należących do Matrix0.

Krok 8: Konfiguracja urządzenia - obwód Matrix1

Krok 9: Konfiguracja urządzenia - 3-bitowy licznik binarny

Górna część układu zawiera elementy logiczne, głównie 3-bitowy licznik binarny, taktowany przez wyjście ADC INT, jak już omówiono. Licznik ten jest zaimplementowany za pomocą dość „standardowego” schematu pokazanego na rysunku 12.

Licznik ten realizowany jest w naszym projekcie za pomocą Flip-Flops DFF9, DFF10, DFF11 oraz INV1, LUT4, LUT8. Wyjście DFF9 to LSB, podczas gdy DFF11 to MSB, jak pokazano na rysunku 13.

LUT4 jest skonfigurowany jako XOR, podczas gdy LUT8 wykonuje logikę AND-XOR z rysunku 12.

Wyjścia liczników są połączone z trzema cyfrowymi pinami wyjściowymi w celu zaadresowania zewnętrznego multipleksera analogowego.

LUT10 dekoduje kod licznika po zakończeniu skanowania i wysyła impuls do Matrix0 przez DLY8 i port P12. Osiąga się to po prostu przez połączenie AND z wyjściami licznika, dekodując w ten sposób liczbę 7 dec (0b111 binarny, koniec pętli).

Krok 10: Konfiguracja urządzenia - 3-bitowa logika porównania

Rysunek 15 pokazuje obwód używany do wykrywania, kiedy pętla iteruje pod bieżącym adresem „zwycięzcy”. W takim przypadku, jak już omówiono, impuls cyfrowy powinien wymusić ponowne załadowanie bieżącego wyniku ADC, aby rozwiązać możliwą sytuację zakleszczenia.

Adres „zwycięzcy” jest przechowywany w tymczasowym rejestrze Matrix1 (patrz niżej), natomiast aktualny adres jest wyprowadzany przez licznik binarny.

Bramki XNOR zapewniają prawdziwe (logiczne 1 lub „wysokie”) wyjście, gdy oba wejścia są równe. AND - podanie tego sygnału dla wszystkich bitów (LUT9) daje nam impuls, gdy oba kody binarne są takie same. Szczegóły dotyczące bramek XOR jako kontrolera parzystości można znaleźć w podręczniku.

Sygnał „Counter-equals-Latch” jest przekazywany do Matrix0 przez port P11.

Krok 11: Konfiguracja urządzenia - cyfrowe porównywanie logiki i rejestru tymczasowego

Dolna część rysunku 11 (zaznaczona na rysunku 16) pokazuje blok DCMP, część decyzyjną tego projektu.

DFF6, 7 i 8 tworzą rejestr 3-bitowy do przechowywania tymczasowego numeru wejściowego „zwycięzca” podczas działania pętli. Wejściem do przerzutników są 3-bitowe wyjścia liczników binarnych, jak widać w globalnym obwodzie Matrix 1 na rysunku 11, tutaj pominiętym dla jasności.

Wyjścia tego rejestru nie mogą bezpośrednio sterować 7-segmentowym wyświetlaczem, ponieważ wartość zapisana tutaj zmienia się podczas skanowania i powinna być uważana za „ważną” dopiero na końcu samego skanowania.

Z tego powodu wyjścia rejestrów tymczasowych łączą się z rejestrem pętli Matrix0 przez porty między matrycami P13, P14 i P15.

Ważne jest, aby zaobserwować na rysunku 16, że rejestr tymczasowy jest taktowany przez wyjście DCMP OUT+, gdy porównanie rejestrów ADC-SPI powoduje znalezienie nowego maksimum.

Ten sam sygnał OUT+ jest przekazywany do Matrix0, SPI CLK Logic, przez port P10.

Krok 12: Konfiguracja urządzenia - Właściwości składników macierzy 1

Rysunki 17-19 pokazują okna właściwości komponentów należących do Matrix1.

Krok 13: Wyniki

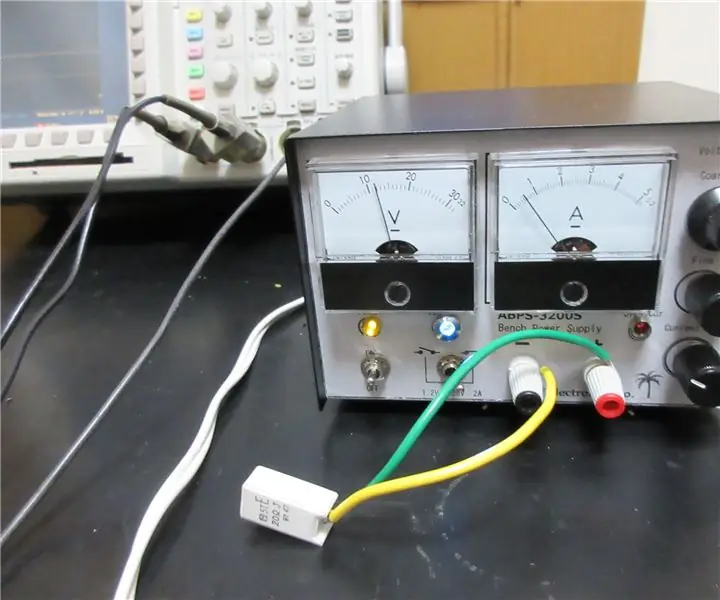

Aby przetestować implementację, skonstruowano prototyp płytki ewaluacyjnej, w której 8 analogowych napięć wejściowych jest uzyskiwanych przez szereg dzielników rezystorowych z TrimPots (jak pokazano na rysunku 20).

Zastosowany multiplekser to ADG508, część, która może pracować przy pojedynczym zasilaniu (12 V).

7-segmentowy sterownik wyświetlacza to 74LS47. Dekoduje równoległe słowo wejściowe i bezpośrednio steruje 7-segmentowym wyświetlaczem ze wspólną anodą.

Płytka ewaluacyjna ma złącze kątowe 2x10, które można podłączyć bezpośrednio do platformy GreenPAK Advanced Development Platform na złączu rozszerzającym, jak pokazano na rysunku 21.

W połączeniu z platformą GreenPAK Advanced Development Platform bardzo łatwo jest wykonywać pomiary sygnałów w celu szybkiego sprawdzenia. Na przykład rysunek 22 przedstawia zestaw sygnałów (odpowiednio CLOCK, wyjście ADC INT i wyjście DCMP OUT+) przechwycone przez analizator stanów logicznych HP 54620A. Przebiegi są wyzwalane przez narastające zbocze sygnału OUT+ (na oscyloskopie oznaczonym jako „A>B”), stąd jest to przechwytywanie przebiegu po wykryciu nowego maksymalnego napięcia między wejściami analogowymi. W rzeczywistości uzyskano to poprzez obrócenie jednego z potencjometrów TrimPots płytki ewaluacyjnej w celu zwiększenia odpowiedniego napięcia pokazanego na rysunku 22.

Rysunek 23 przedstawia schemat Rady Oceniającej.

Wniosek

W tym Instructable wdrożyliśmy ośmiokanałowy wykrywacz maksymalnego (lub minimalnego) napięcia, który ma być używany jako wspólny dodatek do wielokanałowych systemów sterowania. Przedstawione podejście wykorzystuje zaawansowane funkcje komponentów GreenPAK i pokazuje, jak można zintegrować w jednym chipie funkcje analogowe i cyfrowe. Kilka komercyjnych układów scalonych można zastąpić zestawami Dialog GreenPAK, dzięki czemu można zmniejszyć rozmiar aplikacji i koszty.

Zalecana:

LEDura - Analogowy zegar LED: 12 kroków (ze zdjęciami)

LEDura - Analogowy Zegar LED: Po długim czasie robienia różnych projektów postanowiłem sam zrobić instruktażowy. W przypadku pierwszego przeprowadzę Cię przez proces tworzenia własnego zegara analogowego z niesamowitym adresowalnym pierścieniem LED. Wewnętrzny pierścień pokazuje godziny, ou

Monitor napięcia dla baterii wysokonapięciowych: 3 kroki (ze zdjęciami)

Monitor napięcia dla akumulatorów wysokiego napięcia: W tym przewodniku wyjaśnię, jak zbudowałem monitor napięcia akumulatora dla mojego elektrycznego longboardu. Zamontuj go tak, jak chcesz i podłącz tylko dwa przewody do akumulatora (Gnd i Vcc). W tym przewodniku założono, że napięcie akumulatora przekracza 30 V, w

DIY analogowy zasilacz stołowy o zmiennej wysokości z precyzyjnym ogranicznikiem prądu: 8 kroków (ze zdjęciami)

DIY analogowy zasilacz stołowy z precyzyjnym ogranicznikiem prądu: W tym projekcie pokażę, jak używać słynnego LM317T z tranzystorem mocy z wzmacniaczem prądu oraz jak używać wzmacniacza z czujnikiem prądu Linear Technology LT6106 do precyzyjnego ogranicznika prądu. Ten obwód może umożliwić możesz używać do więcej niż 5A

Termometr analogowy Arduino DIY: 7 kroków (ze zdjęciami)

Termometr analogowy Arduino DIY: Drodzy przyjaciele, zapraszamy do kolejnego samouczka! Dzisiaj dowiemy się, jak używać tego analogowego woltomierza z Arduino i wyświetlać temperaturę zamiast napięcia. Jak widać, w tym zmodyfikowanym woltomierzu możemy zobaczyć temperaturę w de

Cyfrowy termometr Picaxe z maks. i min.: 13 kroków

Cyfrowy termometr Picaxe z wartością Max i Min: (Proszę zostawić wiadomość, ale nie bądź zbyt krytyczny, to jest moja pierwsza instrukcja!!) Jest to termometr, który zrobiłem dla naszego samochodu kempingowego, aby pokazać temperaturę zewnętrzną. Opiera się na chipie Picaxe, ponieważ są tanie i łatwe w użyciu. Jeśli to jest dla