Spisu treści:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:27.

- Ostatnio zmodyfikowany 2025-01-23 15:02.

JDM jest popularnym programatorem PIC, ponieważ wykorzystuje port szeregowy, minimum komponentów i nie wymaga zasilania. Ale jest tam zamieszanie, z wieloma odmianami programisty w sieci, które z nich współpracują z jakimi PIC? W tej „instrukcji” poddaliśmy testowi JDM i pokazuję, jak symulować obwód za pomocą Spice, który odpowie na wszystkie Twoje pytania!

Kieszonkowe dzieci

LTspice, który można pobrać z Analog Devices tutaj.

Potrzebujesz tutaj również plików obwodów JDM.

Krok 1: Wymagania dotyczące portu szeregowego

JDM wymaga portu szeregowego zgodnego ze specyfikacją EIA232, najlepiej z poziomami napięcia +12/-12.

Zgodnie z arkuszem danych Texas Instruments Line Driver MC1488 (rysunek 3)

Impedancja wyjściowa = 4V/8mA = 500 omów.

Limit prądu zwarciowego =12mV, bez limitu czasowego - brak uszkodzeń chipa.

Impedancja wejściowa odbiornika liniowego = zalecana od 3 kΩ do 7 kΩ.

Porty szeregowe w starszych komputerach stacjonarnych wykorzystują napięcie +12 V/-12 V spełniając to wymaganie.

Porty szeregowe w nowszych laptopach używają niższych napięć. JDM może działać lub nie - odpowiedź jest bardziej złożona.

Krok 2: Wymagania dotyczące programowania PIC

Informacje dotyczące wymagań dotyczących programowania PIC są uzyskiwane z firmy Microchip. Powyższe dotyczy typowego urządzenia.

Krok 3: Specyfikacja JDM

Czy oryginalna strona internetowa JDM zaginęła we mgle czasu? To pozwala nam zgadywać, co projektant pierwotnie zaplanował dla specyfikacji.

- Zapewnij VDD=5V i maksymalnie do IDD=2mA (dla wersji „w gnieździe”)

- Zapewnij VHH=13V i maksymalnie IHH=0.2mA.

- MCLR Czas narastania tVHHR = 1uS max.

- Wersja ICSP musi być w stanie obniżyć MCLR w porównaniu z podciąganiem 22 tys.

Krok 4: Opis obwodu

Rysunek JDM1 jest oparty na „standardowym” obwodzie JDM pobranym ze strony internetowej PICPgm. Jest to programator „PIC in Socket”, w którym PIC pobiera zasilanie z pinów TX i RTS. Oryginalny schemat był trudny do zrozumienia, więc przerysowałem go, stosując normalną konwencję przepływu prądu od góry do dołu. I dodałem wskaźniki LED „RESET”, „PROG” i „RTS”, które są niezbędne podczas budowy i testowania. Miejmy nadzieję, że nie mają one żadnego szkodliwego wpływu na zachowanie.

Normalna konwencja projektowania obwodów jest taka, że wszystkie masy są wspólne, ale kluczową cechą JDM jest to, że masa portu szeregowego (GND) jest podłączona do VDD. Powoduje to zamieszanie, ponieważ sygnały portu szeregowego są mierzone w odniesieniu do GND, sygnały PIC w odniesieniu do masy logicznej (VSS).

Kiedy TX staje się wysoki, Q1 zachowuje się jak dwie diody spolaryzowane do przodu. (Kolektor Q1 nie jest spolaryzowany wstecznie, jak przy normalnej pracy tranzystora). Kolektor Q1 ładuje C2, który jest zaciśnięty na VDD+8V przez Zenera (D3). Nadajnik Q1 dostarcza 13 V do MCLR w trybie programowania/weryfikacji.

Kiedy TX spada, kondensator C3 jest ładowany przez D1, a VSS jest zaciskany na VDD-5V przez Zenera (D5). Również TX jest zaciskany na (VSS-0,6) przez D1. Q1 jest wyłączony, C1 utrzymuje ładunek do następnego impulsu programowania. MCLR jest przyciśnięty do 0V przez D2, więc PIC jest teraz zresetowany.

Gdy RTS jest wysoki, zegar jest przesyłany do PGC. Zacisk D4 PGC przy wysokim poziomie logiki VDD. Gdy RTS jest niski, kondensator C3 jest ładowany przez D6, a VSS jest zaciskany na VDD-5V przez Zenera (D5). D6 zaciska PGC na VSS lub logicznym 0.

Podczas programowania dane wysyłane przez DTR są odczytywane na PGD, który PIC konfiguruje jako dane wejściowe. Gdy DTR jest wysokie, Q2 działa jako „wtórnik emitera”, a napięcie PGD wynosi około (VDD-0,6) lub logiczne 1. Gdy DTR jest niskie, Q2 działa jak zły tranzystor (zamienione piny emitera i kolektora). Q2 obniża PGD, który jest blokowany przez D7 na VSS lub logicznym 0.

Podczas weryfikacji PIC konfiguruje PGD jako wyjście do wysyłania danych do portu szeregowego. DTR musi być ustawiony na wysoki, a dane są odczytywane na CTS. Gdy wyjście PGD jest wysokie, Q2 jest wyłączone, CTS = DTR = +12V. Gdy wyjście PGD jest niskie, Q2 jest włączony. Kolektor Q2 pobiera prąd (12V+5V)/(1k+1k5)=7mA z DTR i obniża CTS do VSS.

Krok 5: Przygotuj się do symulacji

Pobierz spice LT, zapisz i otwórz pliki obwodów (*.asc) dostarczone tutaj. Aby zasymulować obwód, musimy dać mu kilka wejść, a następnie „prześledzić” wyjścia. V1, V2 V3 symulują port szeregowy 12 V z impedancją wyjściową R11, R12, R13.

- V1 generuje 2 impulsy programu na TX od 0.5ms do 4.5ms

- V2 generuje serię impulsów danych na DTR od 1,5 do 4,5 ms

- V3 generuje serię impulsów zegarowych na RTS od 0,5 do 3,5 ms

Komponenty V4, X1, R15 i R16 są częścią symulacji.

- V4 generuje 2 impulsy od 2,5 do 4,5 ms w celu weryfikacji danych.

- Zworka X1 symuluje WYJŚCIE na PGD.

- R15, R16 symulują „ładowanie” PIC na VDD i MCLR.

Krok 6: Modyfikacje dla ICSP

Rysunek JDM3 przedstawia wersję do programowania „w obwodzie”. Modyfikacje oryginału są

- Zamień gniazdo ZIF na złącze ICSP.

- PIC jest teraz zasilany z obwodu docelowego (V5).

- Usuń Zenera 5 V (D5).

- Mały kondensator 100pF (C4) jest przesunięty obok PIC w obwodzie docelowym.

- Tam, gdzie to możliwe, diody LED pobierają energię z płytki drukowanej.

- Rezystor podciągający MCLR (R10) i dioda (D10) są wymagane w obwodzie docelowym.

- OSTRZEŻENIE. Deska celownicza musi mieć „pływające” zasilanie, najlepiej baterię.

- Nie należy podłączać uziemienia docelowego (VSS) do uziemienia komputera/komputera przez podłączenie innych portów komputera w tym samym czasie, co JDM.

Po symulacji JDM1 pojawił się problem długiego czasu ładowania na C2. Następnie po przeczytaniu Fruttenboel okazuje się, że C2 i Q1 zostały dodane jako modyfikacja oryginału. Nie potrafię sobie wyobrazić, co C2 i Q1 mają robić poza stwarzaniem problemów. Tak więc w przypadku JDM4 powracamy do starszego projektu na Fruttenboel, który jest prosty i łatwy do zrozumienia. Zacisk MCLR D1 i D3/LED2 pomiędzy VSS a VDD+8V. Wartość R1 zostaje zmniejszona do 3k3, co wystarczy do zaświecenia diody LED2 przy 12V.

JDM4 jest również przystosowany do pracy ze słabszymi portami szeregowymi. Kiedy TX osiąga wysoki poziom (+9V), źródło prądu TX = (9-8)/(1k +3k3) = 0,2mA, wystarczy, aby podnieść MCLR wysoko, chociaż nie wystarczy, aby oświetlić diodę LED2. Kiedy TX jest niski (około -7V), upływ prądu TX =(9-7)/1k = 2mA. Prąd LED1 = (7-2 dla led)/(2k7) = 1,8mA. Prąd obniżający MCLR = 7-5,5/3k3 = 0,5mA.

Obwód ten został również przetestowany (symulacja JDM5), aby zobaczyć, co dzieje się z portami szeregowymi minimum +/-7V, gdzie napięcie jest niewystarczające do podtrzymania VHH=13V. Cel C1 staje się teraz oczywisty, C1 tworzy krótki +ve boost do MCLR, skok 33us na zboczu narastającym TX, wystarczająco długi, aby PIC mógł wejść w tryb programowania? Ale usuń zworkę X2 (wyłącz diodę LED1), ponieważ prąd jest niewystarczający, aby obniżyć MCLR i jednocześnie zaświecić diodę LED1. Kiedy TX spada, upływ prądu TX = (7V-5,5V)/(1k+3k3) = 0,3mA, wystarczy, aby obniżyć MCLR w stosunku do podciągania R10.

Krok 7: Wyniki symulacji

Aby wyświetlić pliki graficzne, lepiej kliknąć prawym przyciskiem myszy poniższe linki, a następnie wybrać „Otwórz link w nowej karcie”

Symulacja 1: ślad MCLR, VSS i RTS dla oryginalnego JDM1. Natychmiast widoczne są obserwacje 1, 2 i 3.

Symulacja 2: ślad MCLR i VSS oraz RTS dla zmodyfikowanego JDM2, który naprawia poprzednie problemy.

Symulacja 3: ślad PGD, VSS i PGC dla wysyłania danych JDM2 w trybie programowym. Obserwacja 4 przy 3,5mS.

Symulacja 4: ślad PGD, VSS i CTS dla JDM2 w trybie weryfikacji (włożona zworka X1). ok

Symulacja 5: ślad MCLR, VSS, PGD i PGC dla JDM3. ICSP wykorzystujący moc z obwodu rozwiązuje wiele problemów.

Symulacja 6: ślad MCLR, VSS, PGD i PGC dla JDM4 z portem szeregowym +/-9V. MCLR podnosi się natychmiast, w pełni sprawny.

Symulacja 7: ślad MCLR, VSS i TX dla JDM5 z portem szeregowym +/-7V i usuniętą zworką X2. C1 tworzy +ve boost (skok) na zboczu narastającym MCLR, prawie wystarczający, aby zepchnąć MCLR powyżej TX do 13V.

Krok 8: Wnioski

Spice jest naprawdę dobry w ujawnianiu „ukrytych tajemnic” działania obwodów. Najwyraźniej obwód JDM działa i jest kompatybilny z wieloma układami PIC, ale poniższe obserwacje ujawniają możliwe ograniczenia/problemy ze zgodnością/błędy?

- Długi czas narastania MCLR podczas ładowania C2 do VPP przy pierwszym impulsie TX. Nie powiedzie się specyfikacja 3.

- Port szeregowy ładuje C2, gdy TX osiąga wysoki poziom, a RTS spada. Ale RTS ma również za zadanie ładowanie C3. Gdy oba występują w tym samym czasie, powoduje to większe obciążenie RTS, w konsekwencji C3 traci ładunek (wzrost VSS) po 2 ms podczas symulacji. Awaria specyfikacji 1.

- C3 traci ładunek (VSS zaczyna rosnąć) po zatrzymaniu impulsów zegarowych na 3,5 ms.

- Jaki jest cel C2, w ogóle jest potrzebny?

Rozwiązania

- Przypuszczalnie PICPgm korzysta z oprogramowania „obejścia”. Musi zastosować długi impuls TX do wstępnego naładowania do C2, a następnie wejść w tryb programowania dopiero po drugim impulsie TX? Do symulacji zmniejszyłem wartość C2 do 1uF, aby uzyskać czas narastania 1ms. Nie idealne rozwiązanie.

- Podziel C2 i C3, aby ładowały się niezależnie. Jedna mała modyfikacja JDM2, C2 odnosi się do GND zamiast VSS.

- Rozwiązany przez JDM3. ICSP jest znacznie bardziej niezawodny, ponieważ PIC jest zasilany przez obwód docelowy.

- JDM4 rozwiązuje problem 1. Jest to prosty projekt całkowicie eliminujący C2.

Krok 9: I wreszcie

Dowodem na budyń jest jedzenie. Ten JDM działa, więc używaj go dalej.

A moje rekomendacje to:

- użyj JDM2 do programowania gniazd i portów szeregowych 12 V,

- użyj JDM4 dla programatora ICSP i portów szeregowych powyżej +/-9V,

- użyj JDM4 z usuniętą zworką X2 dla portów szeregowych powyżej +/-7V.

Bibliografia:

Przyprawa do urządzeń analogowych LT

picpgm

Fruttenboel

Śledź więcej projektów PIC w sly-corner

Zalecana:

KS-Garden:Przegląd: 9 kroków

KS-Garden:Przegląd: KS-Garden może być używany do nawadniania/wentylacji./oświetlania roślin ogrodowych/szklarniowych na podwórku lub roślin do uprawy w pomieszczeniach (konstrukcja modułowa)System KS-Garden składa się głównie z następujących modułów- Główny skrzynka systemowa - skrzynka przekaźników i zasilaczy

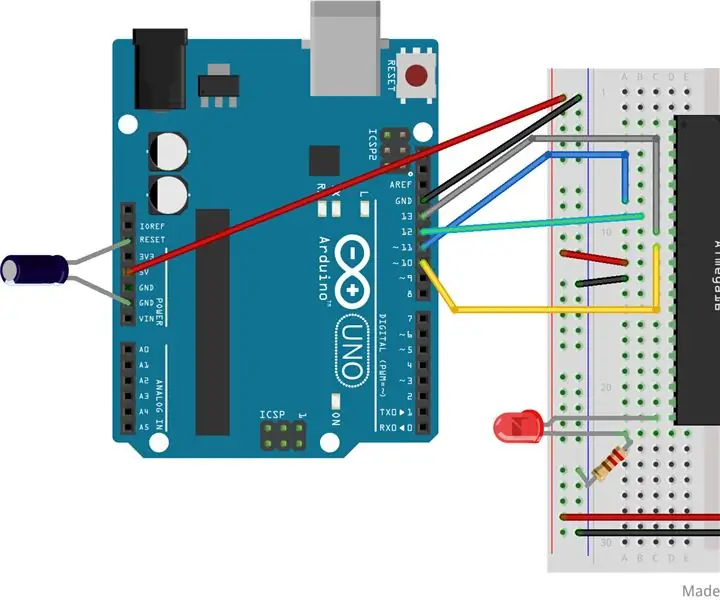

Jak przesłać kod C do ِAVR przy użyciu Arduino Uno jako programisty: 6 kroków

Jak wgrać kod C do ِAVR za pomocą Arduino Uno jako programisty: Cześć wszystkim: D Tutaj podzielę się prostym sposobem zaprogramowania dowolnego układu AVR za pomocą Arduino Uno R3 Wszystko, czego potrzebujesz, aby wypalić kod na mikrokontrolerze, to Arduino Uno zamiast kupować konkretny programista, który dużo kosztuje

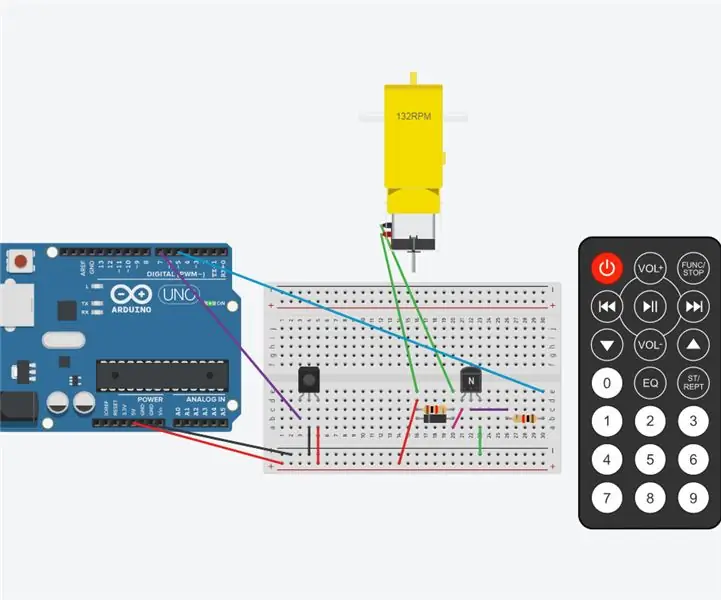

Silnik sterowany tranzystorem z pilotem; przegląd obwodów: 9 kroków

Silnik sterowany tranzystorem z pilotem; Przegląd obwodu: Ten obwód jest silnikiem sterowanym tranzystorowo z pilotem. Pilot włącza zasilanie. Tranzystor włączy silnik. Kod programu zwiększy prędkość silnika i następnie zmniejsz prędkość silnika do zera

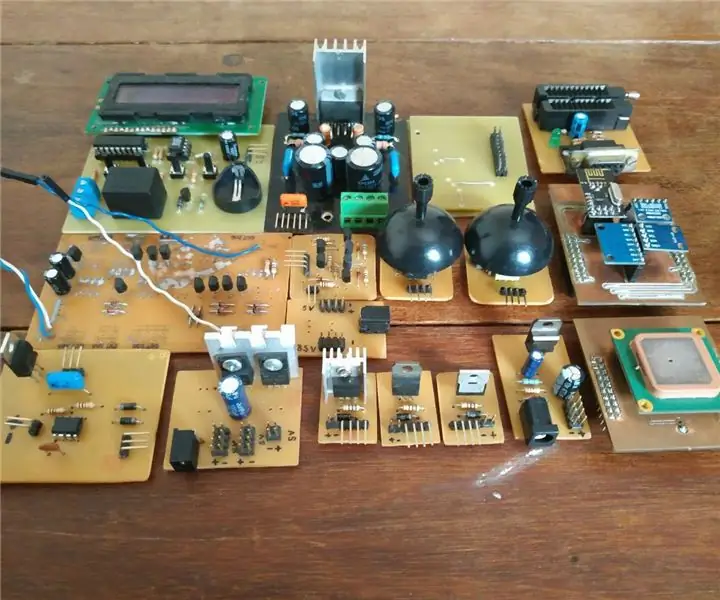

Przegląd projektowania i trawienia PCB: 5 kroków

Projektowanie i trawienie PCB Przegląd: Istnieje kilka sposobów projektowania i trawienia PCB, od najprostszych do najbardziej wyrafinowanych. Tymczasem łatwo się pomylić co do tego, który wybrać, który najlepiej odpowiada Twoim potrzebom.W celu wyjaśnienia niektórych pytań, takich jak t

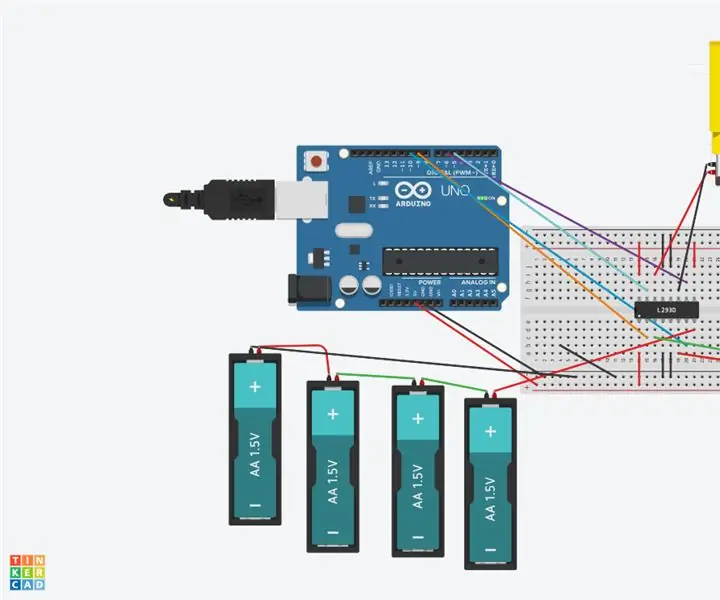

Używanie mostka H (293D) do napędzania 2 motoreduktorów Hobby Ans Arduino; przegląd obwodów: 9 kroków

Używanie mostka H (293D) do napędzania 2 motoreduktorów hobbystycznych Ans Arduino; przegląd obwodu: mostek H 293D to układ scalony, który może napędzać 2 silniki. Zaletą mostka H nad obwodami sterującymi tranzystorowymi lub MOSFET jest to, że może napędzać 2 silniki dwukierunkowo (do przodu i do tyłu) za pomocą kodu;