Spisu treści:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:27.

- Ostatnio zmodyfikowany 2025-01-23 15:02.

W tym samouczku napiszemy kod Verilog do sterowania serwomotorem. Serwo SG-90 jest produkowane przez firmę Waveshare. Kupując serwosilnik, możesz otrzymać arkusz danych zawierający napięcie robocze, maksymalny moment obrotowy i proponowaną modulację szerokości impulsu (PWM)… itd. Jednak FPGA DuePrologic zapewnia napięcie wejściowe 3,3V, podczas gdy napięcie robocze serwomechanizmu SG-90 wynosi 5V - 7V. W przypadku braku zasilania elektrycznego wymienię mój skalibrowany PWM, aby pomyślnie obrócić serwomotor.

Nasze zadanie: Serwomotor obraca się tam i z powrotem z okresem 5 sekund

Pełne menu:

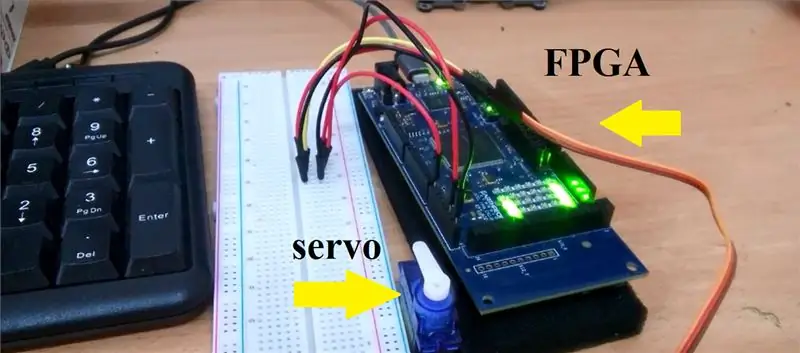

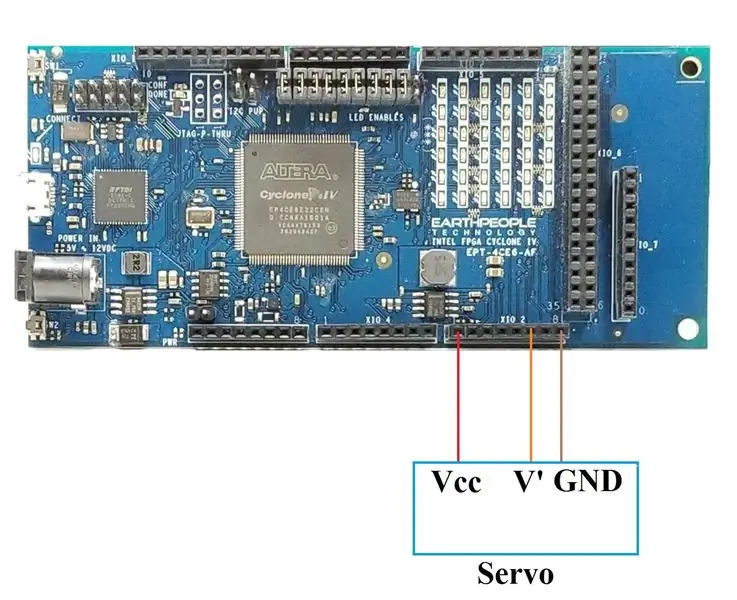

Krok 1: Zbuduj obwód elektroniczny

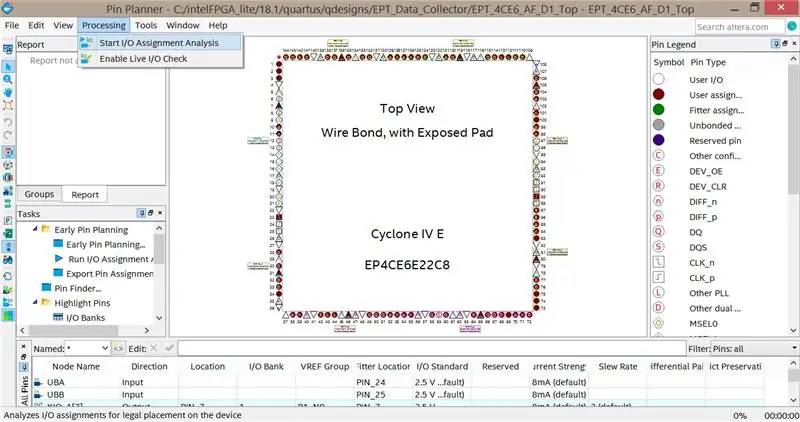

Krok 2: Skonfiguruj Pin Planner

Kliknij „Rozpocznij analizę przypisania we/wy”, aby sprawdzić, czy planer pinów jest ustawiony prawidłowo. W przeciwnym razie musisz samodzielnie zaimportować wszystkie nazwy portów.

Krok 3: Kod Verilog

Tworzymy timer "servo_count". Gdy „servo_A” jest WYSOKIE, PWM wynosi 1,5 ms, a zatem serwo znajduje się na 120 st. C. W przeciwieństwie do tego, gdy „servo_A” jest LOW, PWM wynosi 0,15 ms i dlatego serwo jest utrzymywane na poziomie 0 stopni.

przypisz XIO_2[3] = servo_pulse; //dla V'

reg [31:0] licznik_serw;

początkowy początek

servo_count <= 32'b0;

serwo_A <= 1'b0;

kończyć się

zawsze @(posge CLK_66)

rozpocząć

servo_count <= servo_count + 1'b1;

if(servo_count > 40000000) //Cykl zegara 66MHz, 1/66M * 400000000 ~ 5 sekund

rozpocząć

serwo_A <= !serwo_A;

servo_count <= 32'b0;

kończyć się

kończyć się

reg [31:0] ex_auto;

początkowy początek

ex_auto <= 32'b0;

servo_auto <= 1'b0;

kończyć się

zawsze @(posge CLK_66)

rozpocząć

if(serwo_A==1'b1)

rozpocząć

ex_auto <= ex_auto + 1'b1;

if(ex_auto > 100000) //Cykl zegara 66MHz, ten PWM to ~1.5ms, serwo obraca się do 120 stopni

rozpocząć

serwo_auto <= !serwo_auto;

ex_auto <= 32'b0;

kończyć się

kończyć się

jeśli(serwo_A==1'b0)

rozpocząć

ex_auto <= ex_auto + 1'b1;

if(ex_auto > 10000) //Cykl zegara 66MHz, to PWM ~0.15ms, serwo obraca się do 0 stopni

rozpocząć

serwo_auto <= !serwo_auto;

ex_auto <= 32'b0;

kończyć się

kończyć się

kończyć się

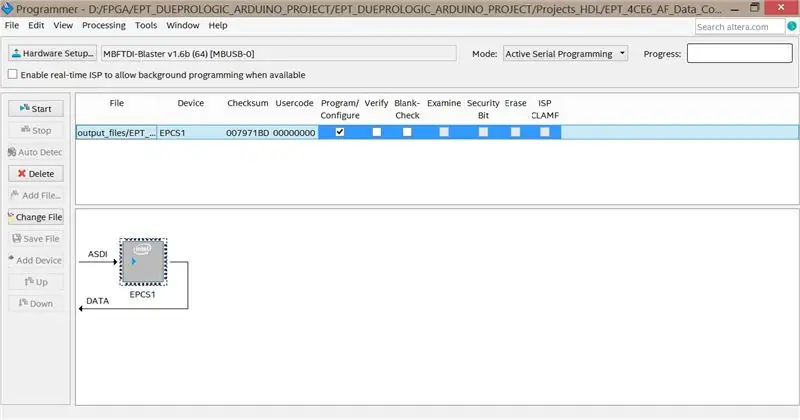

Krok 4: Prześlij kod Verilog

Kliknij „Rozpocznij kompilację”. Jeśli nie jest wyświetlany żaden komunikat o błędzie, przejdź do „Programisty”, aby zakończyć konfigurację sprzętu. Pamiętaj, aby w razie potrzeby zaktualizować plik pof w "Zmień plik". Kliknij „Start”, aby przesłać kod.

W końcu powinieneś zobaczyć, że serwomotor jest okresowo obracany.

Zalecana:

FPGA Cyclone IV DueProLogic steruje kamerą Raspberry Pi: 5 kroków

FPGA Cyclone IV DueProLogic steruje kamerą Raspberry Pi: Pomimo tego, że FPGA DueProLogic jest oficjalnie zaprojektowane dla Arduino, zamierzamy udostępnić FPGA i Raspberry Pi 4B. W tym samouczku zaimplementowano trzy zadania:(A) Jednocześnie naciśnij dwa przyciski na FPGA, aby odwrócić kąt

FPGA Cyclone IV DueProLogic - przycisk i dioda LED: 5 kroków

FPGA Cyclone IV DueProLogic - Przycisk i dioda LED: W tym samouczku użyjemy układu FPGA do sterowania zewnętrznym obwodem diody LED. Zamierzamy wykonać następujące zadania (A) Użyj przycisków na FPGA Cyclone IV DuePrologic do sterowania diodą LED. (B) Dioda Flash włączona & okresowo wyłączaj Demo wideo Lab

Jak zrobić system Wi-Fi, który steruje oświetleniem i ogrzewaniem akwarium: 5 kroków?

Jak zrobić system Wi-Fi, który steruje oświetleniem i ogrzewaniem akwarium: Co robi? System, który automatycznie włącza / wyłącza akwarium zgodnie z harmonogramem lub ręcznie za pomocą przycisku lub żądania internetowego. System, który monitoruje temperaturę wody i wysyła wiadomości e-mail oraz alerty w przypadku

Samouczek: Jak Arduino steruje wieloma urządzeniami o tym samym adresie za pomocą multipleksera TCA9548A I2C: 3 kroki

Samouczek: Jak Arduino kontroluje wiele urządzeń o tym samym adresie za pomocą multipleksera TCA9548A I2C: Opis: Moduł multipleksera TCA9548A I2C umożliwia podłączenie urządzeń o tym samym adresie I2C (do 8 tego samego adresu I2C) podłączonych do jednego mikrokontrolera. Multiplekser pełni funkcję strażnika, przerzucając polecenia do wybranego zestawu

Kontrolowane przez FPGA ramię robota z serwomotorem RC - Digilent Contest: 3 kroki

Sterowane przez FPGA ramię robota z serwosilnikiem RC - Digilent Contest: ramię robota z serwosilnikiem sterowane przez FPGA Celem tego projektu jest stworzenie programowalnego systemu, który może wykonywać operacje lutowania na płycie perforowanej. System oparty jest na płytce rozwojowej Digilent Basys3 i będzie w stanie lutować ko